# **TABLEOFCONTENT**

# Contents:

#### MODULE-1:8085MICROPROCESSORS

- 1. INTRODUCTION:

- 2. IMPORTANTFEATURESOF 8085MICROPROCESSORS:

- 3. PINDIAGRAMOF8085MICROPROCESSORS:

- 4. PINDESCRIPTIONOF8085 MICROPROCESSORS:

- 5. INTERNALARCHITECTUREOF8085MICROPROCESSORS:

- 6. INSTRUCTIONSETSOF8085 MICROPROCESSORS:

- 7. ADDRESSINGMODEOF8085 MICROPROCESSORS:

- 8. PROGRAMMINGFOR8085MICROPROCESSORS

- a) ASSEMBLYLANGUAGEFOR8BITADDITION:

- ASSEMBLYLANGUAGEPROGRAMMINGFOR8BITADDITIONUSINGMEMORYLOCATION:

- c) ASSEMBLYLANGUAGEPROGRAMMING FOR8BITMULTIPLICATIONRESULTING 16BITNUMBER:

- d) ASSEMBLYLANGUAGEPROGRAMMINGFORDIVISIONOF8BITBYA8BITNUMBER:

- e) PROGRAMFORFINDINGTHESMALLESTNUMBERRFROMAGIVEN DATA:

- f) PROGRAMTOFINDTHELARGESTNUMBERFROMAGIVENDATAARRAY:

- g) PROGRAMFORBINARYTOGRAYCOADCONVERSION:

- 9. TIMINGDIAGRAMOF8085MICROPROCESSORS:

- 10. STACKANDSUBROUTIN:

- 11. MULTIPLECHOICEQUESTIONANDANSWER:

- 12. ASSIGNMENT:

#### **MODULE-2:8086MICROPROCESSORS**

- 1. IMPORTANTFEATURESOF 8086MICROPROCESSORS:

- 2. PINDIAGRAMOF8086MICROPROCESSORS:

- 3. PINDESCRIPTIONOF8086 MICROPROCESSORS:

- 4. INTERNALARCHITECTUREOF8086MICROPROCESSORS:

- 5. INSTRUCTIONSETSOF8086 MICROPROCESSORS:

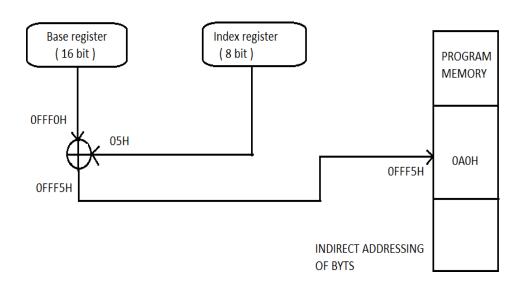

- 6. ADDRESSINGMODEOF80865 MICROPROCESSORS:

- 7. PROGRAMMINGFOR8086MICROPROCESSORS:

- 8. MINIMUMMODECONFIGURATIONOF8086MICROPROCESSORS:

- 9. MAXIMUMMODECONFIGURATIONOF8086MICROPROCESSORS:

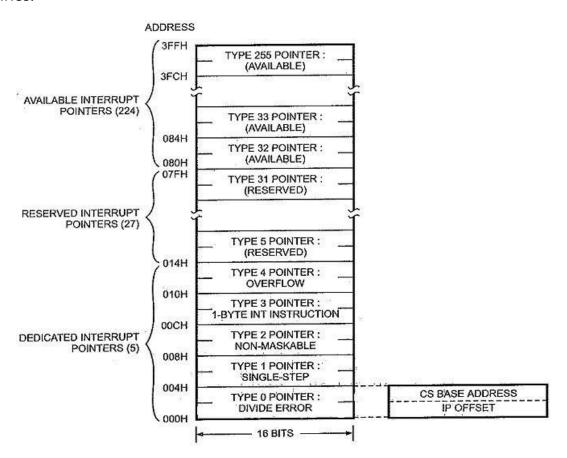

- 10. INTERRUPTSTRUCTUREOF8086MICROPROCESSOR:

- 11. MULTIPLECHOICEQUESTIONANDANSWER:

- 12. ASSIGNMENT:

#### MODULE-3:INTERFACINGDEVICES

- 1. INTRODUCTION:

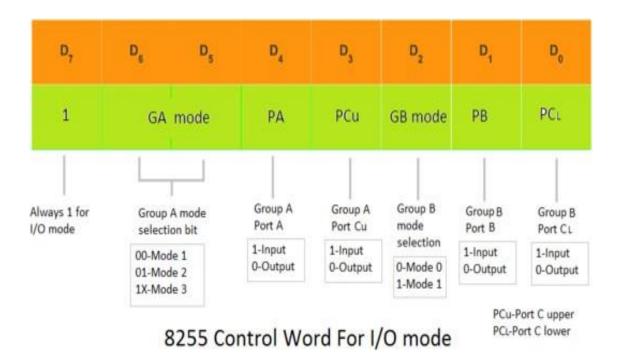

- 2. 8255PPI(PROGRAMMABLEPERIPHERALINTERFACE):

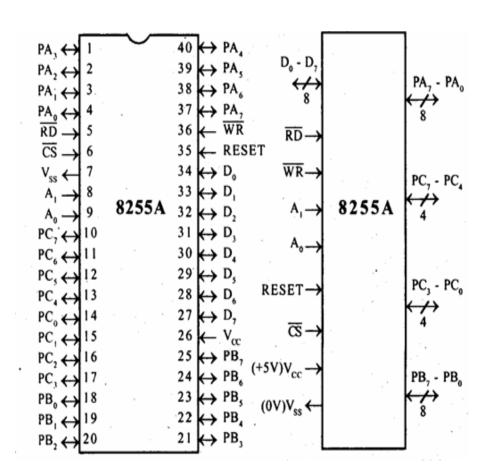

- ➤ PINDIAGRAMOF8255PPI:

- ➤ PINDESCRIPTIONOF8255 PPI:

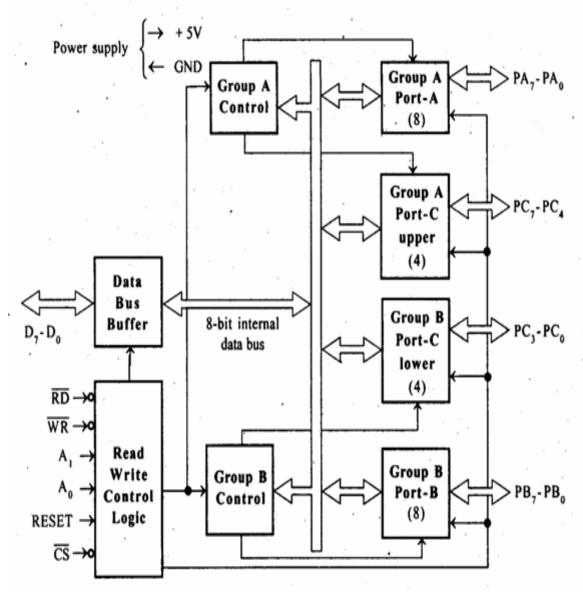

- ➤ INTERNALARCHITECTUREOF8255PPI:

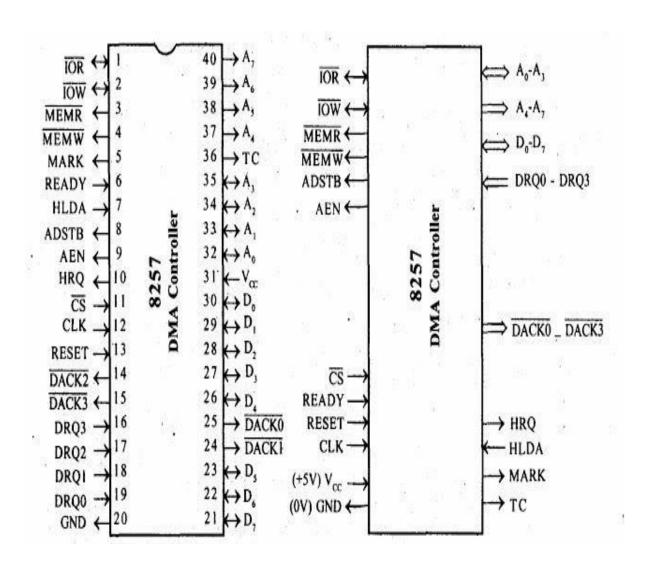

- 3. 8257DMA(DIRECTMEMORYACCESS):

- ➤ PINDIAGRAMOF8257DMA:

# **TABLEOFCONTENT**

- ➤ PINDESCRIPTIONOF8257 DMA:

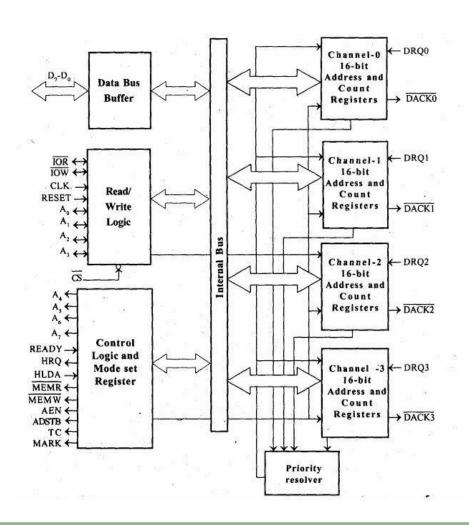

- ➤ INTERNALARCHITECTUREOF8257DMA:

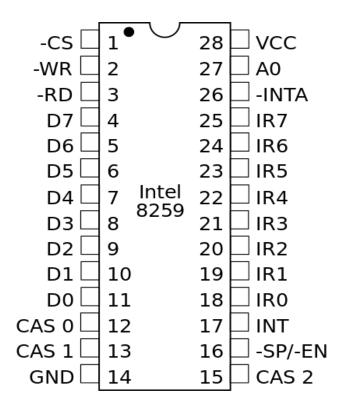

- 4. 8259PIC(PRIORITYINTERRUPTCONTROLLER):

- ➤ PINDIAGRAMOF8259PIC:

- ➤ PINDESCRIPTIONOF8259 PIC:

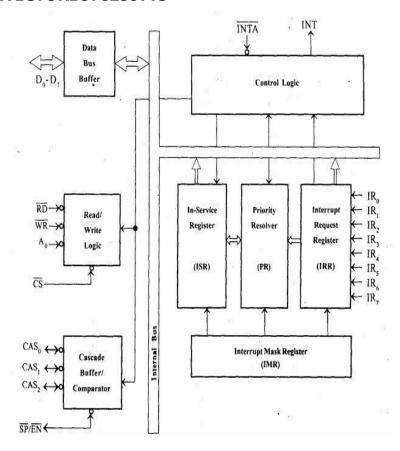

- > INTERNALARCHITECTUREOF8259PIC:

- 5. 8251USART(UniversalSynchronousAsynchronousReceiverTransmitter):

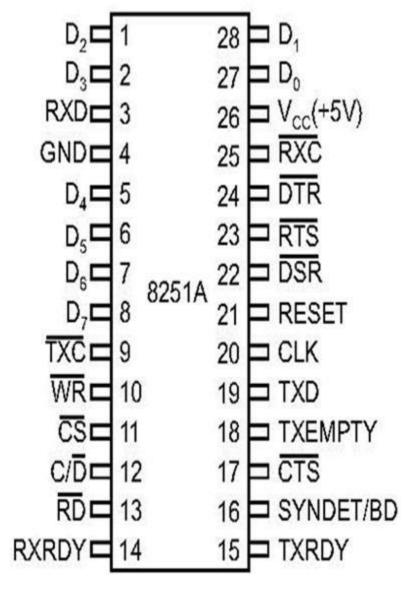

- ➤ PINDIAGRAMOF8251USART:

- ➤ PINDESCRIPTIONOF8251 USART:

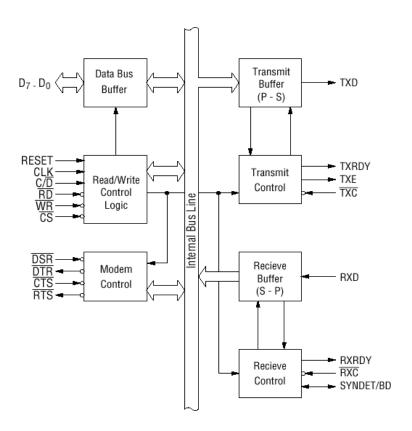

- ➤ INTERNALARCHITECTUREOF8251USART:

- 6. SERIALDATATRANSFERFORMAT:

- 7. INTERFACINGPROBLEM:

- 8. MULTIPLECHOICEQUESTIONANDANSWER:

- 9. ASSIGNMENT:

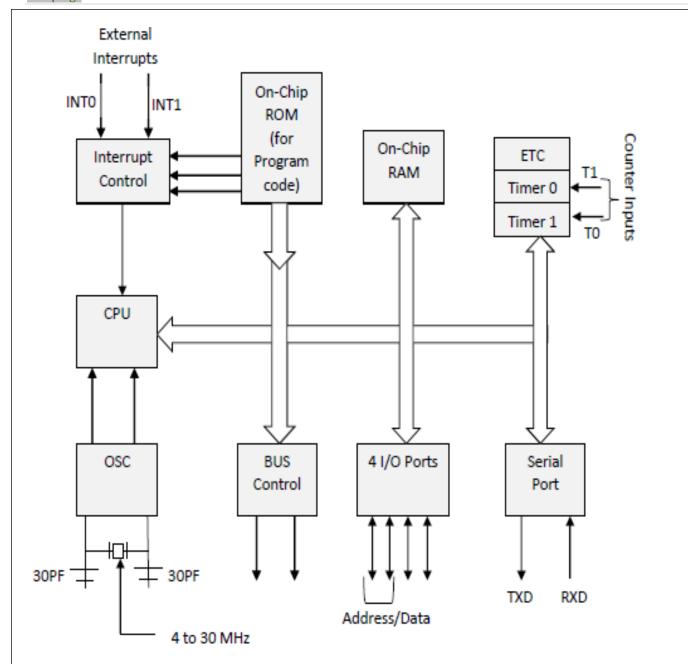

#### MODULE-4:8051MICROCONTROLLERS

- 1. INTRODUCTION:

- 2. PINDIAGRAMOF8051MICROPROCESSORS:

- 3. PINDESCRIPTIONOF8051 MICROPROCESSORS:

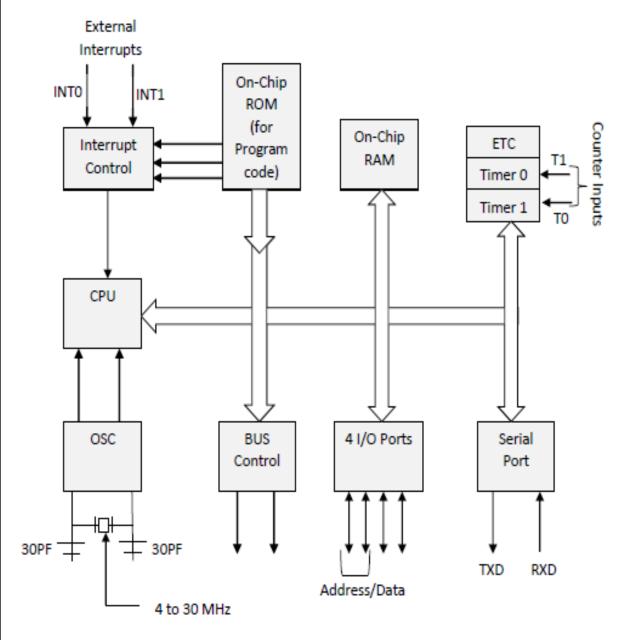

- 4. INTERNALARCHITECTUREOF8051MICROPROCESSORS:

- 5. INSTRUCTIONSETSOF8051 MICROPROCESSORS:

- 6. ADDRESSINGMODEOF8051 MICROPROCESSORS:

- 7. MULTIPLECHOICEQUESTIONANDANSWER:

- 8. ASSIGNMENT:

#### MODULE-5: MAXIMUM MODE CONFIGURATION

- 1. INTRODUCTION:

- 2. DIRECT MEMORY ACCESS

- 3. DIGITAL TO ANALOG CONVERTER

- 4. ANALOG TO DIGITAL CONVERTER

- 5. PROGRAMMING OF 8051 TIMERS

- 6. 80386 AND 80486 MICROPROCESSOR

- 7. ASSIGNMENT:

# **MODULE-1:8085MICROPROCESSORS**

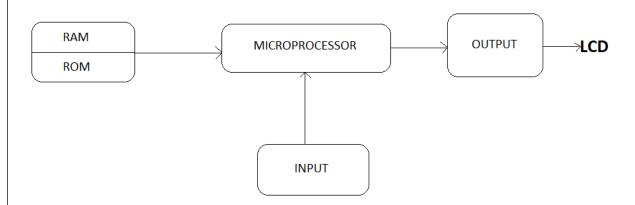

**Introduction:**Itismultipurpose,programmable,clockdriven,registerbased,electronicsdevice thattakesthedataintheformofbinary,processesandthe resultisdisplayedatoutputdevice or LCD display.

# Importantfeaturesof8085Microprocessor:

- The 8085 microprocessor is an 8-bit processor that means its dataline is 8-bit and address line is 16-bit.

- Its internal clock frequency is up-to 5MHz so that the processor takes about 0.2µsec to complete an instruction.

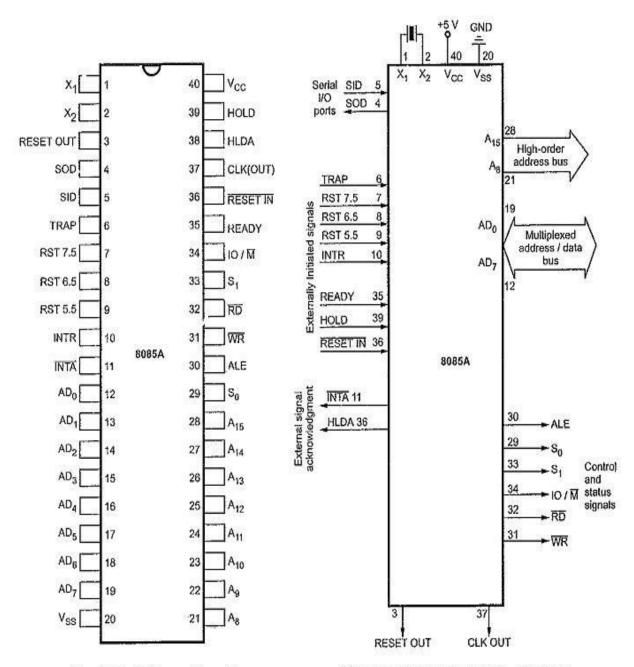

# Pindiagramof8085 Microprocessor:

Fig. 1.3 (a) Pin configuration

Fig. 1.3 (b) Functional pin diagram

# Pindescriptionfor8085Microprocessor:

Itconsistsof40 pinsandoperates at+5V DC.

#### X1&X2

• Pinno-1&2areusedasX1&X2respectively.

• These are two external pins which are connected to an external crystal oscillator which provides an internal clock frequency up-to 5MMHz to the processors of takes about 0.2 µsec to compute an instruction.

#### **RESETIN'&RESETOUT**

- Pinno-36&3areusedasRESETIN'&RESETOUT' respectively.

- Thesepinsarebasicallyusedtorestarttheprocessor iftheprogramhangsinbetween.

#### **SOD**

- Pinno-4is usedasSerialOutputDatapin.

- $\bullet \quad Through this pinthed at a from the processor is send to the output device or LCD screen. \\$

#### **SID**

- Pinno-5isusedas SerialInputDatapin.

- ThroughthispinwecantransferthedatafromIOdevicetotheprocessor.

### **TRAP**

- Pinno-6isusedas TRAPpin.

- Itisanon-maskableinterruptthatmeansitsbit lineisalwayshighandtherearenologic gatesorflipfloptocontrolthisinterrupt.Sooncethisinterruptisactivatedtheprocessor willstopthecurrentprogramandjumptosomeotherprogramwhichisrequiredatthat specific moment of time and till the completion of that specific program the processor cannot return back to original program.

# RST7.5,RST6.5&RST5.5

- Pinno-7, 8& 9areusedasRST7.5, RST6.5&RST5.5 respectively.

- Thesearethemaskableinterruptpins.

- Oncethisinterrupt isactivated the processor will stop the current program and jump to some other program which is required at that specific moment of time and till the completion of that specific program the processor return back to original program.

#### **INTR**

- Pinno-10isusedasInterruptRequest pin.

- Thispinisusedtoreceiveaninterrupt requestsignal. It is a type of maskable interrupt.

#### INTA'

• Pinno-11isusedasINTA'(Interruptacknowledgement)pin.

Iftheinterruptisactivatedthentheprocessorwillsendanacknowledgemessagethrough INTA'

pin i.e. INTA'=0, INTA=1.

## AD0-AD7&A8-A15

- Pinno-12topinno-19areusedasbothdatalineandaddresslinepin(AD0-AD7).

- Pinno-21topinno-28areusedasaddresslinepin(A8-A15).

- Thatmeansin8085 microprocessorshave8-bitdatalineand16-bitaddressline.

## **VSS**

Pinno-1isusedasVSSorGNDpin.

### S0&S1

- Pinno-29andpinno-33isusedforS0&S1respectively.

- These are 2 status signal pins which are basically used to check read, write and opcode operation, where S1 is used for memory read operation and S0 is used for memory write operation.

| <b>S</b> 1 | S0 | OPERATION |

|------------|----|-----------|

| 0          | 0  | HALT      |

| 0          | 1  | WRITE     |

| 1          | 0  | READ      |

| 1          | 1  | FETCH     |

#### **ALE**

• Pinno-30isusedasALE(AddressLatchEnable)pin.

#### WR'

- Pinno-31isusedasWR'pin.

- Itisusedforwriteoperation(WR'=0,WR=1).

- $\bullet \quad It is basically used to separate the address from the address \ and databus.$

#### RD'

- Pinno-32isusedas RD'pin.

- Itisareadsignalusedfor readoperation. Itisalsoan activelow signal

# IO/M'

- Pinno-34is usedforInputOutput/Memory' pin.

- If the data is transferred to one processor to another processor then it is IO operation. So, in that case IO/M'=1

- If the data is transferred within the processor itself that means either the data is transferred toaccumulator or to some other memory address or register sointhat case it is either a memory read or memory write operation so IO/M'=0.

## **READY**

- Pinno.-35isusedasREADYpin.

- This is an acknowledgment signal from the slower I/O devices or memory.

- Whenhigh, it indicates that the device is ready to transfer data, else the microprocessor is in the wait state.

#### **CLK**

- Pinno-37is usedas CLK pin.

- Thispintellsabouttheclock pulse.

- ThroughthispinwecanconnecttootherdigitallCpinsandbasicallyusetoprovide square wave pulse or clock pulse or clock frequencies.

### **HOLD& HLDA**

- Pinno-38isusedas HLDAandpinno-39 isusedas HOLDpin.

- Once the HOLD pin is activated then the processor will not allow any external data to interferethecurrentprogramandiftheholdissuccessfullyactivated then the processor will send an acknowledge message through the HLDA pin.

#### **VCC**

- Pinno-40isusedasVCCpin.

- ThroughVCCpin+5VDCsupply isprovided to the IC.

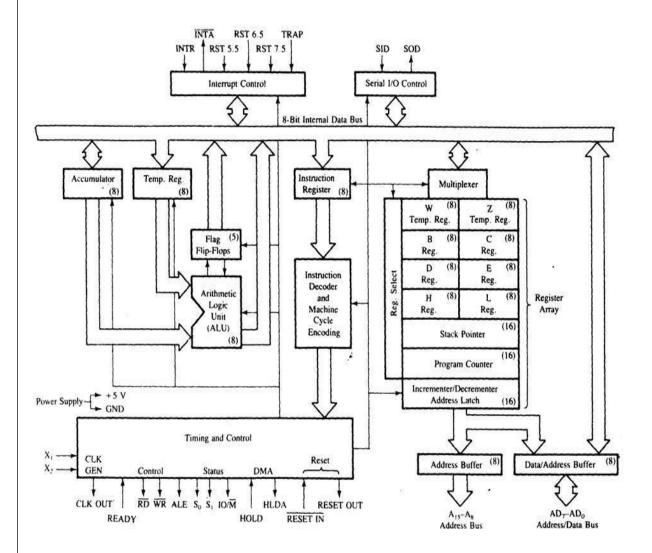

# INTERNALARCHITECTUREOF8085MICROPROCESSOR

The total internal architecture of 8085 microprocessor can be divided into 3 major units they are;

# i. ArithmeticandLogicUnit(ALU):

The main function of ALU is to perform arithmetic operation such as addition, subtraction, multiplication and division etc. and logical operation such as AND, OR, EX-OR etc.

To ALU 3 other sub units are attached which helps in performing different arithmetic and

logical operation they are:

# A. Temporaryregister:

The main function of temporary register is to store the data temporary before the data is transforming to ALU to performing different arithmetic and logically units.

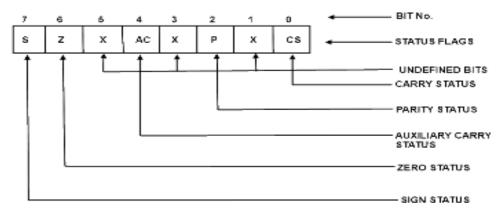

# **B. Statusflag:**

Figure 2: Status Flags of Intel 8085

The main function of status flag is to check the status of the output program or to checkwhethertheresultisrightorwrong. It consists of 8-bitout of which 5 are active flags and three re undefined bits.

- ➤ **Sineflag:**Afterthearithmeticoperationiftheresultisnegativethensign flag is tends to logic 1 otherwise it will tend to logic 0.

- ➤ **Zeroflag:**Afterthearithmeticoperationiftheresultiszerothenzeroflag will tend to logic 1 otherwise it will tend to logic 0.

- ➤ **Auxiliaryflag:**Afterthearithmeticoperationifthereisacarryfrom3<sup>rd</sup>to 4<sup>th</sup>bitthenauxiliarycarrywilltendstologic1otherwiseitwilltendtologic 0.

- ➤ **Parityflag:**Afterthearithmeticoperationiftheresultofthesumcontains evenno. of1'sthenparityflagwilltendtologic1otherwiseitwilltendto logic 0.

- ➤ **Carry flag:** After the arithmetic operation if the result is more than 8 bits then there will be a carry from 7-8 bit so carry flag will tends to logic 1.

#### C. Accumulator:

The final result of a rithmetic and logical operation is stored in accumulator.

# ii. Setsof register:

Registers are temporary storing device and acts as flip flop. We can store the data in register temporarily and we can delete it. In 8085 microprocess or the reare 6 general purpose and the register of th

register they are B, C, D, E, H, L and each register can store 8-bits of data individually that meansBcanstore8-bitofdata,Ccanstore8-bitsofdataandsoon.Butinpairformi.e.BC, DE, HL ARE STORES 16-bits of data. This are known as general purpose register because in most of the programming we use these registers commonly for storing 16-bits or 8-bitsof data.

# **♣**Special purpose register

These are 16-bits registers which are used for some specific purpose. The special purpose registers are:

# A. Stackpointer

- Stack: Stack is a set of memory location whose address is different from main memory. We can transfer the data from main memory to stack memory by push instruction and we can retrieve the data from stack memorytomainmemorybypopinstruction. The data transform from main memorytostack memory by FIFO (Firstin First Out) sequence and is retrieve from stack memory to main memory by LIFO (Last in Last Out) sequence.

- To locate a particular memory address, we take the help of stack pointer and is given by LXI SP, 9904- load the content of stack pointer into the memory address 9904.

# **B.** Programcounter

Itholdstheaddressofthenextinstructionoritcheckswhethertheaddress for next instruction is available or not.

# C. Incrementdecrementlatch

o Itisbasically used for incrementand decrement operation.

# iii. Timingandcontrolunit:

Themainfunction of timingandcontrol unitsistocheck howmuchtimethe processor will taketoexecutetheoperation. To the timing and control unit an external crystal oscillatoris attached which provide and internal clock frequency up-to 5 MHz. So that the processor will take a specific amount of time i.e. T=1/F, here F=5 MHz so T=0.2 µsec time is taken by the processor to execute the operation.

Tothetimingandcontrolunitstwootherunitsareattachedtheyareinstructionregisterand instruction decoder.

**Instruction registers:** The main function of instruction registers is to store to opcode of an instruction.

**Instruction:**Instructionsaresetofcommandgiventotheprocessortoperformaspecific operation.

e.g.MVIA,38

Eachinstructionhas2partsi.e. opcodeandoperand

- **Opcode**:Thefirstpartofinstructionwhichspecifiessometaskwedonebytheprocessor. Here MVI is the opcode which means move immediately the data.

- **Operand**:The second part of instruction which is basically used to store the data or to perform a memory read or memory write operation.

- ✓ Memory read: When the data is transfer to accumulator then that is the memoryread operation.

- ✓ **Memory write:** When the data is transferred to some other memory address apart from accumulator then that is memory write.

Instructiondecoder: Its main function is to convert them nemonics to its machine code.

**Mnemonics:** Mnemonicsaretheliterallanguageunderstoodbyuser-oruser-friendly language.

# INSTRUCTIONSETSOF8085MICROPROCESSORS

Instructionsaresets of commands given to the processor to perform aspecific operation. Each instruction can be defined into two parts on eistheoperate and another isoperand.

- **According to word length:** Word length means the no. of bits or bytes a specific instruction occupies. Accordingly, there are 3-types i.e.1-byte, 2-byte, 3byte.

- a) 1-byte: In 1-bytes instruction the opcode is define but the operand data is not directly specified but is specified by some register.

e.g. ADD B- In this case the opcode is defined i.e. ADD which has got a machine code of 8-bit, but the operand is specified by register so it is 1-byte instruction.

- **b) 2-byte:**In2-byteinstructionopcodeispresentfollowedby8-bitoperanddata. e.g.MVIA,30-Inthiscasetheopcodeisdefinedi.e.MVIwhichhasgotamachine codeof8-bit and theoperand datais 30 whichhas thebinaryvalue00110000 i.e. 8-bit. So, the total size is 16-bits and called 2-byte instruction.

- **c) 3-byte:**In3-byteinstructiontheopcodeispresentandfollowedby16-bitoperand data. e.g.STA9100-Inthis casethe opcodeis definedi.e.STAwhichhas got amachine codeof8-bitandtheoperanddatais9100whichhasthebinaryvalue

1001000100000000 i.e. 16-bit. So, the total size is 24-bits and called 3-byte instruction.

- **According to operation:** according to the type of operation it performs the total instruction sets can be classified into 5 different types, they are

- a) Datatransforminstruction: It is basically used for transferring the data from one register to another register or register to memory without changing the content. E.g. MOVA, B-Move the content of Bregisters to accumulator. MOV A, 34<sub>H</sub>-Move the 8-bit data 34<sub>H</sub> to accumulator.

- **b) Arithmeticinstruction:** These are basically used for arithmetic operationsuch as addition, subtraction, multiplication, division, increment, decrement etc. In this case the final result may change.

- e.g.ADDB-Addthecontent ofregisterBwiththeaccumulator.

- c) Logical instruction: These instructions are basically used for logical operation such as ANA (AND), ORA (OR), XRA (XOR), CMP (COMPARE) etc.

- **d) Branch control instruction:** The instruction under this group are basically used for conditional or unconditional jump operation.

E.g.

- JNZ- Jump if the counter data in the register C is not zero to label loop.

JNC- Jump if there is no carry or borrow to label loop.

- **e) IO and machine control:** The instruction under this group are basically used for controlling the device or for transferring the data from one device to another deviceorforset orresetofthestatusflagorforstack operationcomesunderthis group. e.g.HALT(tostoptheprogram)

INO2 (to receive the data from port 02)

OUT01(totransferdatathroughport01) STC

(set the carry flag to logic-1)

# ADDRESSINGMODEOF8085MICROPROCESSOR

Itisthetechniquethroughwhichwearespecifyingdataforoperationorhowtheoperanddata is specified accordingly in 8086 microprocessors. There are 8 different addressing mode according to the type of operation it performs.

- 1. Registeraddressingmode

- 2. Immediateaddressing mode

- 3. Directaddressingmode

- 4. Registerindirectaddressingmode

- 5. Implicitaddressing mode

- **1. Register addressingmode:** Inthistypeof addressing modetheoperand datais not directly specified in the instruction itself but it is specified by some register. E.g.MOVA,B-Movethe contentofBregistertoaccumulator.

- 2. Immediateaddressingmode:Inthistypeofaddressingmodetheoperanddata is directly specified in the instruction itself.

- E.g. MOIA, 08<sub>H</sub>-Moveimmediatelythedata08<sub>H</sub>toaccumulator.

- **3. Directaddressingmode:**Indirectaddressingmodetheoperandaddressis directly specified in the instruction itself.

- E.g.STA9100-Storedthecontentofaccumulatortomemoryaddress9100.

- **4. Registerindirectaddressingmode:**Inthistypeofaddressingmodetheoperand data is not directly transferred to the accumulator; at first it stored in some memory address and the transferred to the accumulator.

- E.g.LXIH,9100-Loadthecontent of HLpair into the memory address 9100 to accumulator.

- **5. Implicit addressing mode:** There are certain instruction through which we can automaticallycomparewiththepreviousvalueofaccumulatorandtheinstruction under this group comes under implicit addressing mode.

- E.g.CMPM-Comparethecontent ofmemorywithaccumulator.

- RAL- Rotate the content of accumulator to left by 1-bit.

- RAR-Rotatethecontentof accumulatortorightby1-bit.

| BEL | <b>MNEMONICS</b> | <b>OPERANDS</b> | COMMENT                                                                                   |

|-----|------------------|-----------------|-------------------------------------------------------------------------------------------|

|     | MVI              | A,49            | Move immediately the data $49_H$ to accumulator A.                                        |

|     | MVI              | C, 56           | $\label{eq:movements} Move immediately the data 56_{\text{H}} to register \\ \text{C.}$   |

|     | ADD              | С               | Add the content of register C with accumulator A and the result is stored in accumulator. |

|     | STA              | 9100            | Storethecontentofaccumulatorintothe memoryaddress9100.                                    |

|     | END              |                 | ·                                                                                         |

DATA:

$1^{ST}$ data= $49_H$

$2^{nd}$ data= $56_H$

RESULTinmemorylocation9100=9F

OR

# $\frac{\textbf{ASSEMBLYLANGUAGEPROGRAMMINGFOR8BITADDITIONUSINGMEMORYLOCATI}{\textbf{ON}}$

| LABEL | <b>MNEMONICS</b> | <b>OPERANDS</b> | COMMENT                                                                       |

|-------|------------------|-----------------|-------------------------------------------------------------------------------|

|       | LXI              | H,9100          | Loadthecontent of HL pair into the memory address 9101.                       |

|       | MOV              | A, M            | Move the content of memory to accumulator.                                    |

|       | INX              | Н               | Increment the content of HL pair by next bit.                                 |

|       | ADD              | М               | Add the content of memory with accumulatorandtheresultisstoredin accumulator. |

|       | STA              | 9103            | Storethecontentofaccumulatorintothe memoryaddress9103.                        |

|       | END              |                 |                                                                               |

DATA:

$Memorylocation 9101 = 49_{H}$

$Memory location 9102 = 56_H Result in Memory location 9103 = 9F$

# ASSEMBLYLANGUAGEPROGRAMMINGFOR8BITMULTIPLICATIONRESULTI NG 16 BIT NUMBER.

| LABEL | MNEMONICS<br>MVI | <b>OPERANDS</b><br>E, 05 | <b>COMMENT</b> Moveimmediatelythedata05to register E.                      |

|-------|------------------|--------------------------|----------------------------------------------------------------------------|

|       | MVI              | C, 05                    | Moveimmediatelythedata03to register C which is used for counter operation. |

|       | MVI              | D,00                     | Move the initial data 00 to register D.                                    |

|       | LXI              | H,0000                   | Load the 16-bit data 0000 to HL pair.                                      |

| LOOP  | DAD              | D                        | Add the content of HL pair with DEpairandtheresultisstoredin HL pair.      |

|       | DCR              | С                        | Decrement the content of register C by 1 bit.                              |

|       | JNZ              | "LOOP"                   | Jump till the counter data in register C is not zero to label LOOP.        |

|       | SHILD            | 9105                     | Store the content of HL pair into the memory address 9105 &9106.           |

|       | END              |                          |                                                                            |

# **RESULT:**

Inmemorylocation9105=0F Inmemorylocation9106 =00

# ASSEMBLYLANGUAGEPROGRAMMINGFORDIVISIONOF8BITBYA8BITNUM BER.

| LABEL | MNEMONICS | OPERAND | COMMENT                                |

|-------|-----------|---------|----------------------------------------|

|       | MVI       | A,13    | Move the hexadecimal                   |

|       |           |         | equivalent of 13 to                    |

|       |           |         | accumulator A.                         |

|       | MVI       | B,05    | Move the hexadecimal                   |

|       |           |         | equivalent of 05 to register B.        |

|       | MVI       | C, 00   | Movetheinitialdata00to                 |

|       |           |         | register C, which is                   |

|       |           |         | basicallyused tostorethe               |

|       |           |         | quotient.                              |

| LOOP  | SUB       | В       | Subtract the content of                |

|       |           |         | register B from                        |

|       |           |         | accumulator A and the                  |

|       |           |         | resultisstoredin                       |

|       | INID      |         | accumulator.                           |

|       | INR       | С       | Incrementthecontentof                  |

|       | CMP       | В       | register C by 1 bit.                   |

|       | CIVIP     | D       | Compare the content of register B with |

|       |           |         | register B with accumulator A.         |

|       | JNC       | "LOOP"  | Jumpifthereisnocarryor                 |

|       | J. 13     | 2001    | borrow to label loop.                  |

|       |           |         | 20 to 1000. 100p.                      |

|       | END       |         |                                        |

# **RESULT**:

Quotient is in register= 03<sub>H</sub> Remainderisinaccumulator=04<sub>H</sub>

#### <u>PROGRAMFORFINDINGTHESMALLESTNUMBERRFROMAGIVENDATA</u>LAB MNEMONICS OPERANDS COMMENT EL

| MINEMONICS | OPERANDS | COMMENT                                         |  |  |

|------------|----------|-------------------------------------------------|--|--|

| LXI        | H, 9101  | LoadthecontentofHLpairintothememory             |  |  |

|            |          | address 9101.                                   |  |  |

| MOV        | C,M      | MovethecontentofmemorytoregisterC               |  |  |

|            |          | which is used for counter operation.            |  |  |

| INX        | Н        | Increment the content of memory to              |  |  |

|            |          | accumulator.                                    |  |  |

| MOV        | A, M     | Move the content of memory to the               |  |  |

|            |          | accumulator.                                    |  |  |

| DCR        | C        | DecrementthecontentofregisterCby1 bit.          |  |  |

| INX        | Н        | IncrementthecontentofHLpair address by          |  |  |

|            |          | next bit.                                       |  |  |

| CMP        | М        | Compare the content of memory with accumulator. |  |  |

|            |          |                                                 |  |  |

| JC         | "AHED"   | Jump with carry or borrow to label "AHED".      |  |  |

| MOV        | A, M     | Move the content of memory to                   |  |  |

|            |          | accumulator.                                    |  |  |

| DCR        | C        | DecrementthecontentofregisterCby1 bit.          |  |  |

| JNZ        | "LOOP"   | JumpinthecounterdataintheregisterCis            |  |  |

|            |          | notzerotolabelloop.                             |  |  |

| STA        | 9300     | Storethecontentofaccumulatorintothe             |  |  |

|            |          | memoryaddress 9300.                             |  |  |

| END        |          | ,                                               |  |  |

|            |          |                                                 |  |  |

DATA:

In memory address 9101= 03<sub>H</sub> memory address 9102= 86<sub>H</sub> Inmemoryaddress9103=58<sub>H</sub> Inmemoryaddress9104=75<sub>H</sub>

**RESULT**:

Inmemoryaddress9300=58<sub>H</sub> In

| LABEL | <b>MNEMONICS</b> | <b>OPEANDS</b> | COMMENT                                                                                       |

|-------|------------------|----------------|-----------------------------------------------------------------------------------------------|

|       | LXI              | H,9101         | LoadthecontentofHLpairintothe                                                                 |

|       | MOV              | C,M            | memory 9101.  Move the content of memory to the register C which is used for count operation. |

|       | SUB              | A              | Subtractthecontentofaccumulator fromaccumulator(A=0)andresultis storedinaccumulator.          |

| LOOP  | INX              | Н              | Increment the content of HL pair address by next bit.                                         |

|       | CMP              | M              | Compare the content of memory with accumulator.                                               |

|       | JNC              | "AHED"         | Jump if there is no carry or borrow to label "AHED".                                          |

|       | MOV              | A,M            | Movethecontentofmemorytothe accumulator.                                                      |

| AHED  | DCR              | С              | DecrementthecontentofregisterCby 1 bit.                                                       |

|       | JNZ              | "LOOP"         | Jump till the counter data in register C id not zero to label "LOOP".                         |

|       | STA              | 9105           | Storethecontentofaccumulatortothe memory address 9105.                                        |

|       | END              |                |                                                                                               |

DATA: RESULT:

In memory address  $9101=03_{H}$  memory address  $9102=98_{H}$  Inmemoryaddress  $9103=A5_{H}$  Inmemoryaddress  $9104=29_{H}$

Inmemoryaddress9105=A5<sub>H</sub> In

| PROGRA | <u>PROGRAMFORBINARYTOGRAYCOADCONVERSION</u> |                |                                              |  |  |

|--------|---------------------------------------------|----------------|----------------------------------------------|--|--|

| LABEL  | <b>MNEMONICS</b>                            | <b>OPERAND</b> | COMMENT                                      |  |  |

|        | MVI                                         | A,48           | Moveimmediatelythedata48to accumulatorA.     |  |  |

|        | MOV                                         | C, A           | Movethecontentofaccumulatorto register C.    |  |  |

|        | STC                                         |                | Setthecarryflagtologic-1.                    |  |  |

|        | CMC                                         |                | Complementofcarrybit.                        |  |  |

|        | RAR                                         | С              | Rotatethecontentofaccumulatorto rightby1bit. |  |  |

|        | XRA                                         |                | X-ORofregisterC.                             |  |  |

|        | END                                         |                |                                              |  |  |

RESULT:Graycodeisinaccumulator=6C<sub>H</sub>.

48 -01001000

C -01001000

STC -101001000

CMC-001001001

RAR- 0001001001

XRA- 001101101=>6C

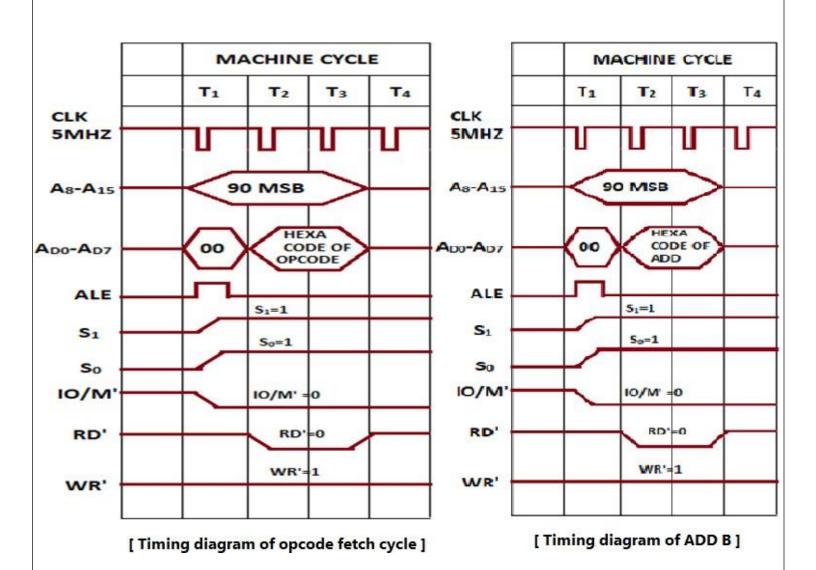

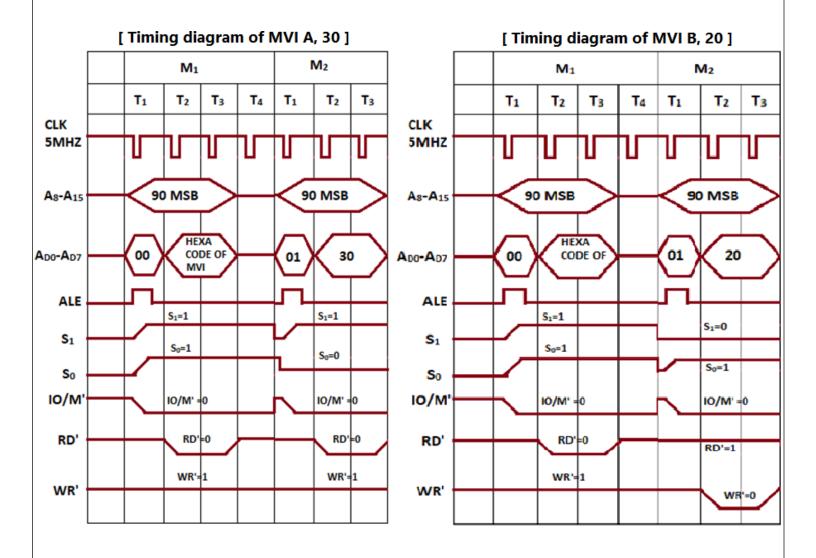

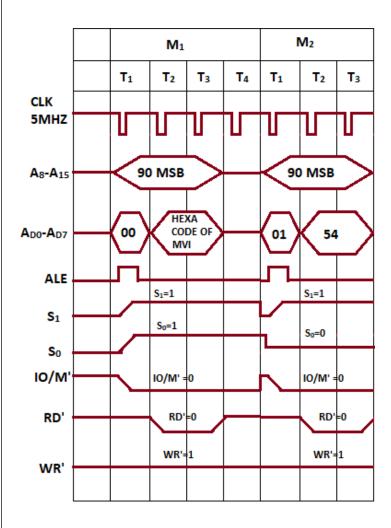

# **TIMING DIAGRAM**

Itisagraphicalrepresentationofinstructioncycleoritshowshowthecontrolsignalsare affected when we are performing an opcode operation r an execution operation.

# Instructioncycle:

Itisthetotaltimerequiredtoreadtheopcodeofaninstructionfromthememoryandto perform the execution operation.

In struction cycle = Opcode fetch cycle + Execution cycle

# Opcodefetchcycle:

It is the total time required to read the opcode of an instruction from the memory. Normallytheopcode fetchcycle hasgotfourT-statesor Timeperiod( $T_1, T_2, T_3, T_4$ )during which a specific operation is being perform.

• **T1-state:**Duringthisstateofmachinecycletheaddressisreadfromthememory.

- **T2 & T3-state:** During these states the hexadecimal code or the machine code of an instruction is read from the memory.

- **T4state-**Thisstateisknownaswaitstateorduringthisperiodthedataistransferred from the opcode fetch cycle to execution cycle.

# Executioncycle:

Itisthetotaltimerequiredtoperformthememoryreadormemorywriteoperation.

In execution cycle the final result is stored so we do not require any <u>wait state</u> (time gap for data overlap).

If the operand data is 8-bit then we required 3T states and if the operand data is 16-bitthen we required 6T states.

- ✓ DuringT1stateofexecutioncycletheaddressisreadfromthememory.

- ✓ DuringT2&T3statesofexecutioncycletheoperanddata isreadfromthememory.

# Q.Iftheexternalclockfrequencyis5MHzthenhowmuchtimetheprocessorwilltaketo execute the operation

- I. MVIA,30

- II. MOVA,B

- III. LXIH,9105

Solution: Givendataf = 5MHz

- I. MVIA,30=  $4T+3T=7T=7*0.2\mu sec=1.4\mu sec$

- II. MOVA,B=  $4T+0T= 4T=4*0.2\mu sec= 0.8\mu sec$

- III. LXIH,9105=  $4T+6T=10T = 10*0.2\mu sec=2\mu sec$

# **Timingdiagramofopcodefetchcycle&ADDB**

# TimingdiagramofMVIA,30&MVIB,20

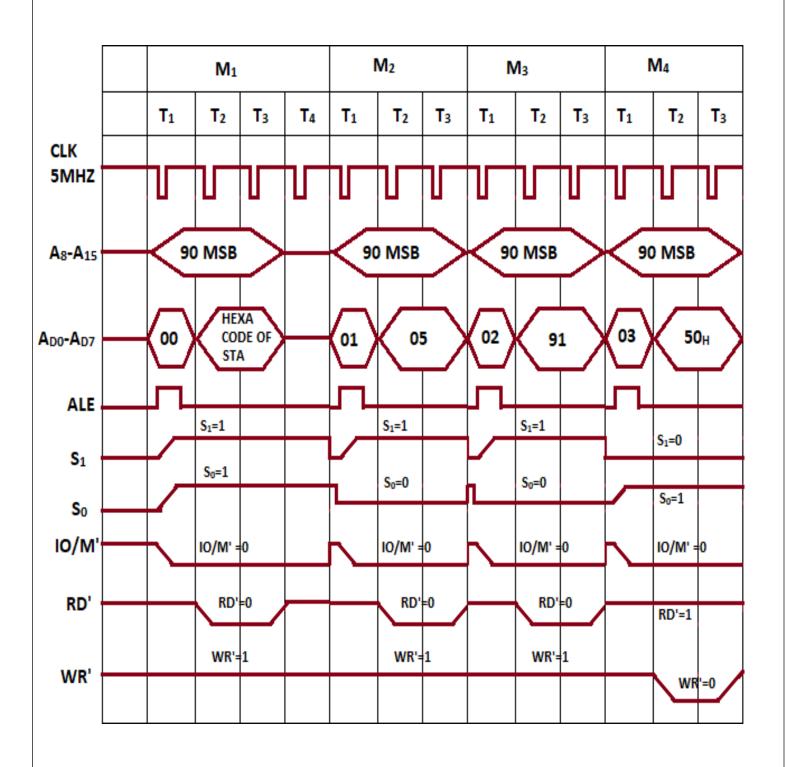

# **TimingdiagramofSTA9105** $M_2$ Мз $M_1$ $T_1$ $T_2$ **T**<sub>3</sub> $T_4$ $T_1$ $T_2$ T<sub>3</sub> $T_1$ T<sub>2</sub> **T**<sub>3</sub> CLK 5MHZ 90 MSB 90 MSB 90 MSB A<sub>8</sub>-A<sub>15</sub> HEXA 05 02 00 01 91 CODE OF A<sub>D0</sub>-A<sub>D7</sub> STA ALE $S_1=1$ $S_1=1$ $S_1=1$ $S_1$ $S_0=1$ $S_0=0$ $S_0=0$ $S_0$ IO/M' IO/M' ≠0 IO/M' =0 IO/M' ≠0 RD' RD'=0 RD'⊨0 RD'=0 WR'**=1** WR'=1 WR'≢1 WR'

# $\underline{Timing diagram of STA 9105 if the accumulator contains 50_{H}}$

#### **STACKANDSUBROUTIN:**

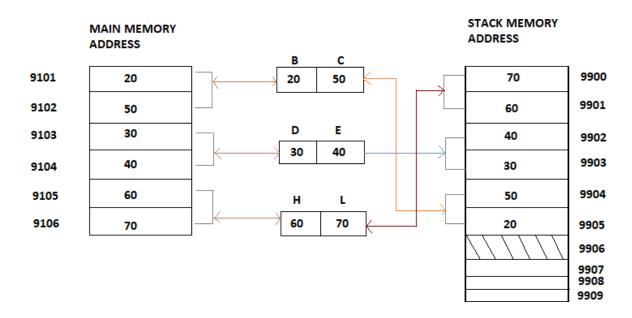

**Stack:**Stackisthesetswhoseaddressisdifferentfrommainmemoryaddress.Wecantransfer the data from main memory to stack memory by PUSH instruction and the data is transferred in FIFO sequence and we can retrieve the data from stack memory to main memory by POP instruction and the data is retrieve by LIFO sequence.

**Subroutine:** Subroutineis asubtaskoritisasmallprograminbetweenthemainprogram.

Q. Initialize the stack memory address 9906. Write a program to transfer the data from mainmemorytostack&thenretrieveit.Supposethedatacontaininmainmemoriesare: 9101-2050<sub>H</sub>, 9103-3040<sub>H</sub>, 9105-6070<sub>H</sub>.

Solution:

| MNEMONICS | OPERAND | COMMENT                       |

|-----------|---------|-------------------------------|

| LXI       | SP,9906 |                               |

| LXI       | B,9901  | Load the data in BC register. |

| LXI       | D,9903  | Load the data in DE register. |

| 0.41        | D   |   |

|-------------|-----|---|

| <b>Z4</b> 1 | Pas | 7 |

| LXI  | H, 9905 | Load the data in HL register.    |

|------|---------|----------------------------------|

| PUSH | В       | Store the data in BC register.   |

| PUSH | D       | Store the data in DE register.   |

| PUSH | Н       | Storethedatainregister.          |

| POP  | Н       | Retrieve the data from register. |

| POP  | D       | Retrieve the data from register. |

| POP  | В       | Retrieve the data from register. |

D)2

| Multiplechoicequestionanswer:                 |  |  |

|-----------------------------------------------|--|--|

| 1. The8085Upis                                |  |  |

| A) 16 bit                                     |  |  |

| B) 8bit                                       |  |  |

| C) 20 bit                                     |  |  |

| D) 32 bit                                     |  |  |

| Answer:B                                      |  |  |

| 2. Theaddresslineof8085upis                   |  |  |

| A) 16 bit                                     |  |  |

| B) 8bit                                       |  |  |

| C) 24 bit                                     |  |  |

| D) noneofthese.                               |  |  |

| Answer: A                                     |  |  |

| 3. ThefunctionofALU is                        |  |  |

| A) Arithmetic operation                       |  |  |

| B) Arithmeticandlogicaloperation              |  |  |

| C) Logicaloperation                           |  |  |

| D) Noneofthese.                               |  |  |

| Answer: B                                     |  |  |

| 4. Thefunctionofcrystal oscillator            |  |  |

| A) providinginternalclockfrequency            |  |  |

| B) impedancematching                          |  |  |

| C) reducingspeed                              |  |  |

| D) Disconnectingports                         |  |  |

| Answer: A                                     |  |  |

| 5. The no.Ofgeneral-purposeregisterin8085upis |  |  |

| A)6                                           |  |  |

| B) 5                                          |  |  |

| C)4                                           |  |  |

| D)3                                           |  |  |

| Answer:A                                      |  |  |

| 6. Theno.Ofaddressingmodein8085 upis          |  |  |

| A)5                                           |  |  |

| B) 4                                          |  |  |

| C)3                                           |  |  |

Answer:A

| Answer:A                                     |

|----------------------------------------------|

| 7. The no.Ofinstructionsetin8085upis         |

| A)4                                          |

| B) 3                                         |

| C)5                                          |

| D)2                                          |

| Answer:C                                     |

| 8. Theno.Ofinterruptin8085 upis              |

| A) 5                                         |

| B) 6                                         |

| C) 7                                         |

| D) 256                                       |

| Answer:A                                     |

| 9. Timingdiagramis                           |

| A) interfacing                               |

| B) connecting                                |

| C) Analyzing.                                |

| D) Graphicalrepresentationofinstructioncycle |

| Answer: D                                    |

| 10. MVIA,30is                                |

| A) Immediateaddressing mode                  |

| B) Implicit                                  |

| C) Direct                                    |

| D) Indirect                                  |

| Answer: A                                    |

| 11. Theno.Ofpinin8085up is                   |

| A) 40.                                       |

| B) 30                                        |

| C) 28                                        |

| D) 32                                        |

| Answer:A                                     |

| 12. Theinterrupthaving highestpriorityis     |

| A) TRAP                                      |

| B) INTR                                      |

| C) RST0                                      |

| D) RST1                                      |

| 13. Theclockatwhich80i85upoperateis           |  |  |

|-----------------------------------------------|--|--|

| A) 4MHz                                       |  |  |

| B) 6                                          |  |  |

| C) 5.                                         |  |  |

| D) Noneofthese                                |  |  |

| Answer: C                                     |  |  |

| 14. MVIA,30is                                 |  |  |

| A) 2Byteinstruction                           |  |  |

| B) 1                                          |  |  |

| C) 3                                          |  |  |

| D) 4.                                         |  |  |

| Answer:A                                      |  |  |

| 15. MOVA,Bis                                  |  |  |

| A) 1Byteinstruction                           |  |  |

| B) 2                                          |  |  |

| C) 4                                          |  |  |

| D) 3                                          |  |  |

| Answer:A                                      |  |  |

| 16. TheinstructionSTAA.9000His                |  |  |

| A) 3Byteinstruction.                          |  |  |

| B) 1.                                         |  |  |

| C) 2.                                         |  |  |

| D) Noneofthese                                |  |  |

| Answer: A                                     |  |  |

| 17. The Instruction LXIH, 9100 His            |  |  |

| A) 2Byteinstruction.                          |  |  |

| B) 3.                                         |  |  |

| C) 4                                          |  |  |

| D) Noneofthese                                |  |  |

| Answer: B                                     |  |  |

| 18. TheinstructionMOVA,Bis                    |  |  |

| A) Directaddressingmode                       |  |  |

| B) indirectaddressing mode                    |  |  |

| C) Immediateaddressing mode                   |  |  |

| D) Registeraddressingnode                     |  |  |

| Answer: D                                     |  |  |

| 19. The no.OfTstatesininstructionisMVIA,30His |  |  |

- A) 4

- B) 7

- C) 10

- D) Noneofthese.

Answer: B

- 20. Theinstructioncycleconsistof

- A) opcodefetchcycle.

- B) opcodefetchcycleandexecutioncycle.

- C) executioncycle

- D) Noneofthese.

Answer: B

# ASSIGNMENT FULL MARKS-100 SECTION-A (ANSWERALLQUESTIONS)

# **Shortanswer type question:**

2\*8=16

- a) Whatarethedifferenttypes of addressing modes in 8085 microprocessor?

- b) Which opcode is used to transfer and which opcode is used to retrieve the data from main memory to stack memory?

- c) Howmanyno. ofmachinecycles are require to execute the instruction MVIA, 47?

- d) GivesomeexampleoflOandmachinecontrolgroup instruction.

- e) Explainthetermsopcodeandoperandinaninstructionwithexample.

- f) Draw the table of status code of 8085 microprocessor and indicate the read, write, halt and fetch operation.

- g) Whatisthefunctionofprogramcounterin8085microprocessor.

- h) Explainthedifferentregistersin8085microprocessor.

#### **SECTION-B**

Focusedanswertypequestion:

6\*6=36

- a) Whatisinterruptoperation? Whatarethe different interrupt pins are in 8085 microprocessor and how they work?

- b) Explainthestatusflagofthe8085microprocessor.

- c) Whatistimingdiagram?DrawthetimingdiagramofMVIA, B.

- d) Writeaprogramtoconvert abinarycodeto graycode.

- e) ExplaintheT-statesinopcodefetchcycleandexecutionfetch cycle.

- f) Explainsomeimportantfeaturesof8085microprocessor.

## **SECTION-C**

# Longanswertypequestion:

16\*3=48

a) Withpropersketchdescribetheinternalarchitectureof8085microprocessor.

b)

- (i) Explainthetermstackandsub-routine. Suppose the data content of main memory,  $BC=2050_{H}$ ,  $DE=1234_{H}$ ,  $HL=2640_{H}$ . Write a program to initialize the stack memory address at  $9080_{H}$  and transfer the data from main memory to stack memory and retrieve it.

- (ii) Iftheexternalclockfrequencyis5MHzthenhowmuchtimetheprocessorwilltake to execute an operation,

- MVIA,30

- MOVA,B

- LXIH,9105

- ADDB

c)

- (i) Writeanassemblylanguageprogramfor8-bitmultiplicationresultinga16-bit number.

- (ii) DrawthetimingdiagramofLXIH,9100ifthedatacontentinthe registeris0756<sub>H</sub>.

# **MODULE-2:8086MICROPROCESSORS**

# Importantfeaturesof8086Microprocessor:

- Itisa16bitprocessorthatmeansitsdatalineis16bitandaddresslineis20bit.

- Itconsists of40pinICchipandoperatesat +5VDC.

- Itcanoperatein3differentclockfrequenciesi.e.5MHz,8MHzand 10MHz.

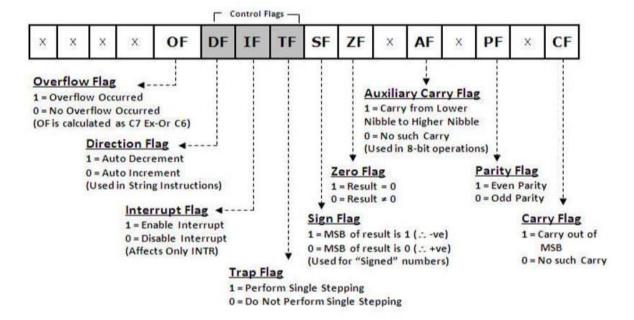

- Itconsistsof9activestatusflagsoutofwhich6areconditionalflagand3are control flag.

| 8085                                                                                                                                                                                                                                                                                                                                                                                                                | 8086                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>The 8085 microprocessor is an 8-bit processor that means its data line is 8 bit and address line is 16 bits.</li> <li>It operates in 3-5MHz clock frequency.</li> <li>It consists of 5 active status flags.</li> <li>It consists of single unit and there is no division in architecture takes place.</li> <li>It consists of single mode and basically used for simple input output operation.</li> </ol> | <ol> <li>It is a 16-bit processor or that means its data line is 16 bit and address line is 20 bits.</li> <li>It can operate in 3 difference CLK frequencies i.e. 5MHz, 8MHz, 10MHz.</li> <li>It consists of 9 active status flags outofwhich6 areconditionalflag and 3 are control flag.</li> <li>The total internal architecture can be divided into 2 different units theyarethebusinterfaceunitand execution unit.</li> <li>Itcanoperatein2differentmodes i.e.minimummodeandmaximum mode.</li> </ol> |

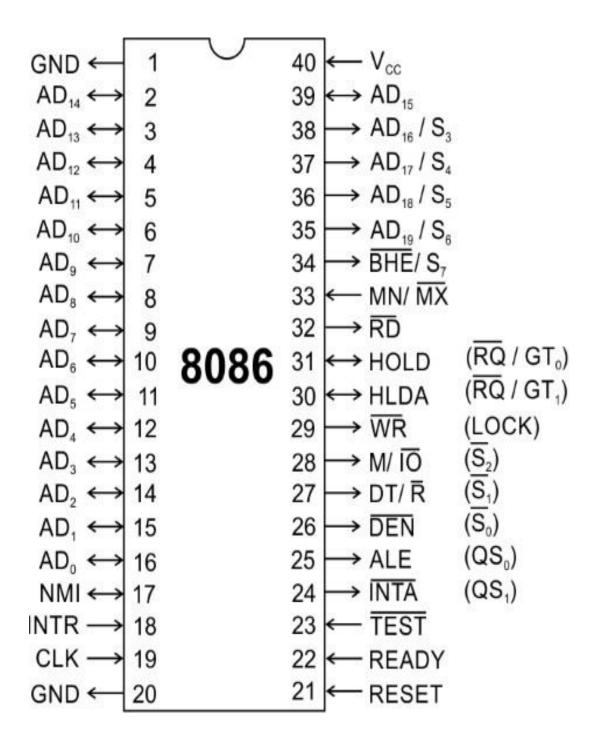

# Pin diagramof8086Microprocessor:

# Pindescriptionfor8086Microprocessor:

Itconsists of 40 pins and operates at +5 VDC.

#### **GND**

• There aretwogroundpinsinthe8086,pin1andpin20.

#### AD0toAD19

- Pinno-2topinno-16 andpinno-39 arebothused asdataline andaddressline(AD0to AD15).

- Pinno-38topinno-35are usedonlyforthe addressline(AD16toAD19).

#### NMI

- Pinno-17isusedforNon-MaskableInterruptRequest.

- Thefunction of NMIpinissameasthatoftrappinof8085microprocessor.

- Thispinisbasicallyusedforinterruptoperationi.e.tostopthecurrentprogramandjump to some other program and till the completion of that specific program, the processor cannot return by to the original program.

#### **INTR**

- Pinno-18isusedasInterruptRequest pin.

- Thispinisusedtoreceiveaninterrupt requestsignal. Itisatypeofmaskable interrupt.

## **CLK**

- Pinno-19is usedas CLK pin.

- Thispintellsabouttheclock pulse.

- ThroughthispinwecanconnecttootherdigitallCpinsandbasicallyusetoprovide square wave pulse or clock pulse or clock frequencies.

#### **RESET**

- Pinno.-21isusedasRESET pin.

- Byusingthispin,theprogramcontrolreturnstoFFFF0<sub>H</sub>.

- Basically, it is used to restart the processor if the program hangs in between.

#### **READY**

- Pinno.-22isusedasREADYpin.

- Thisisanacknowledgmentsignalfromtheslowerl/Odevicesormemory.

- Whenhigh, it indicates that the device is ready to transfer data, else the microprocessor is in the wait state.

#### TEST'

- Pinno-23isusedas**TEST'**pin.

- Thisisalsoanactivelowsignal. This pinisused forwait instruction when the 8086 is connected with the 8087 microprocessors.

- Normallytheprocessorspeedis fast andI/O devicespeedisslow.So,sometimeweare transferring the data to the processor but the data does not reach to the processor. So, in that case the processor goes to wait state and READY pin becomes *LOGIC 0* or deactivated soin that cases the **TEST**'pinbecomes activated i.e. **TEST'=0** and **TEST=1**. So, the processor goes to wait state.

- Again, when the data reach the process or then READY pin becomes activated or tends to LOGIC1 and TEST' pin becomes deactivated i.e. TEST'=1 and TEST=0.

- READYpinisopposite of **TEST'pin.**

### MinimumandmaximumModePins-

Total8pins,fromPin24topin31workdifferentlyfordifferentmodes(maximumorminimum).

#### Minimummode

- Forsimpleoutputoperationthe8086microprocessorscanoperateinminimum mode and in that case the MN/MX'=1 i.e. MN'=1, MX=0, MX=0, where MN is minimummodeandMXismaximummodeand,inthatcase,theminimummode pins get activated.

- The minimum mode pins are HOLD, HLDA, WR', DT/R', DEN', ALE, INTR', M/IO'.

#### **HOLD& HLDA**

- ◆ Pinno-30isusedas HLDAandpinno-31 isusedasHOLDpin.

- Once the HOLD pin is activated then the processor will not allow any external data to interfere the current program and if the hold is successfully activated then the processor will send an acknowledge message through the HLDA pin.

#### WR'

- ◆ Pinno-29isusedasWR′pin.

- ◆ Itisusedforwriteoperation(WR'=0,WR=1).

### M/IO'

- Pinno-28isusedasmemory/input output pin.

- Ifthedataistransferredwithintheprocessorthen itisamemoryoperation.

### DT/R'

- ◆ Pinno27isusedasDT/R′pin(Datatransfer andreceiverpin).

- ◆ If the DT/R'=1, DT=1, R'=1, R=0, then in that case it is a data transfer or write operationandthedatatransferredfromtheprocessortotheexternallOdevice.

- ◆ If the DT/R'=0, DT=0, R'=0, R=1, then in that case it is a data receiver or read operation and the data received from the external IO device to the processor.

#### **DEN'**

- Pinno-26is usedasDEN'(DataEnable)pin.

- Itisbasicallyusedtocheckthevalidityofthedata.

#### **ALE**

- ◆ Pinno-25isusedasALE(AddressLatchEnable)pin.

- ♦ Itisbasicallyusedtoseparatetheaddressfromtheaddress anddatabus.

#### INTA'

- ◆ Pinno-24isusedasINTA'(Interruptacknowledgement)pin.

- ◆ If the interrupt is activated then the processor will send an acknowledge message through INTA' pin i.e. INTA'=0, INTA=1.

#### Maximum mode

- o For multipurpose operation when more than 1 IC chips are used then the 8086 microprocessors can operates in maximum mode and in that case the MN/MX'=0 i.e. MN=0, MX'=0, MX=1.

- MaximummodepinsareQS<sub>1</sub>,QS<sub>0</sub>,S<sub>0</sub>',S<sub>1</sub>',LOCK',RQ'/GT<sub>1</sub>,RQ'/GT<sub>0</sub>

### QS<sub>1</sub>andQS<sub>0</sub>

■ Pinno24and25areusedasQS₁andQS₀pinrespectively.

These are queue status signals and are available at pin 24 and 25. These signals providethestatus ofinstruction queue. Their conditions are shown in the following table –

| QS <sub>0</sub> | QS <sub>1</sub> | Status                         |

|-----------------|-----------------|--------------------------------|

| 0               | 0               | Nooperation                    |

| 0               | 1               | Firstbyteofopcodefromthe queue |

| 1               | 0               | Emptythe queue                 |

| 1               | 1               | Subsequentbytefromthequeue     |

# $S_0', S_1', S_2'$

• These are the status signals that provide the status of operation, which is used by the Bus Controller 8288 to generate memory & I/O control signals. These are available at pin 26, 27, and 28. Following is the table showing their status –

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Status                   |  |

|----------------|----------------|----------------|--------------------------|--|

| 0              | 0              | 0              | Interruptacknowledgement |  |

| 0              | 0              | 1              | I/ORead                  |  |

| 0              | 1              | 0              | I/OWrite                 |  |

| 0              | 1              | 1              | Halt                     |  |

|   |   |   |             | ı |

|---|---|---|-------------|---|

| 1 | 0 | 0 | Opcodefetch |   |

| 1 | 0 | 1 | Memoryread  |   |

| 1 | 1 | 0 | Memorywrite |   |

| 1 | 1 | 1 | Passive     |   |

#### **LOCK**

• When this signal is active, it indicates to the other processors not to ask the CPU to leave the system bus. It is activated using the LOCK prefix on any instruction and is available at pin 29.

### RQ/GT<sub>1</sub>andRQ/GT<sub>0</sub>

■ These are the Request/Grant signals used by the other processors requestingtheCPUtoreleasethesystembus.Whenthesignalisreceived byCPU,thenitsendsacknowledgment.RQ/GT<sub>0</sub>hasahigherprioritythan RQ/GT<sub>1</sub>.

#### RD'

- Pinno-32isusedas RD'pin.

- Itisareadsignalusedfor readoperation. Itisalsoan activelow signal.

### MN/MX'

- Pinno-33isusedasMN/ MX'

- Thispinisusedforminimumormaximummodeofthemicroprocessor. When this pinis 1, the microprocessor works in minimum mode, and when the pin is at 0, the maximum mode is followed.

### **BHE'/S7**

- Pinno-34isusedasBHE'pin.

- BHE stands for Bus HighEnable. It is an active low signal, i.e. it is active whenit is low. It is used to indicate the transfer of data over the higher order data bus (D8 to D15).

• BHE' decides whether the data bus will carry 16-bit data or 8-bit data. When BHE' is enabled(i.e.0),thenthebuswillcarry16-bitdata,elseonly8-bitdatathroughthelower order data bus lines. It is multiplexed with status pin S7.

#### **VCC**

- Pinno-40isusedasVCCpin.

- ThroughVCCpin+5VDCsupplyisprovidedtothelC.

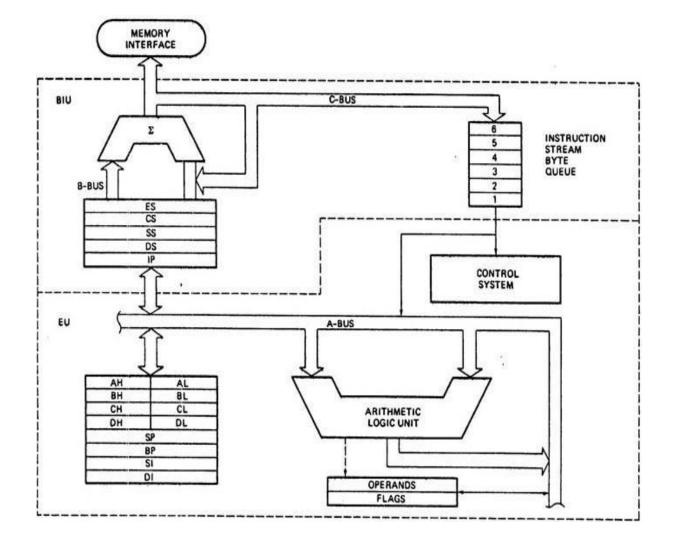

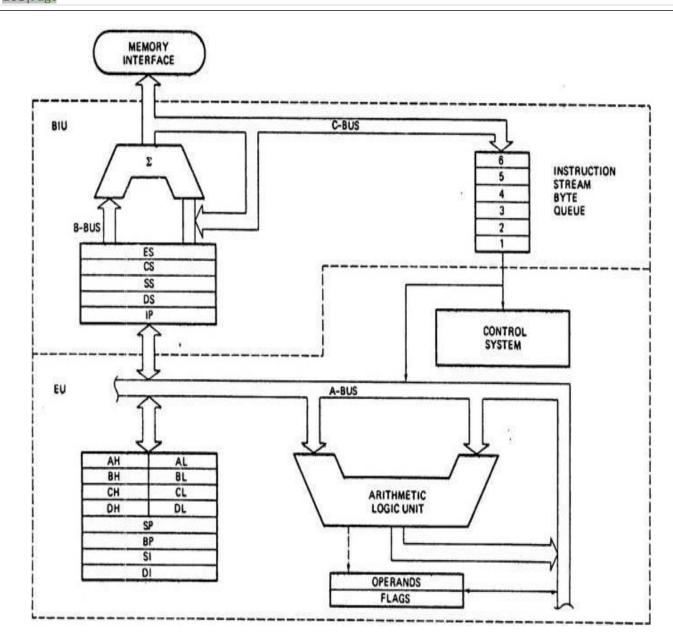

# INTERNALARCHITECTUREOF8086MICROPROCESSOR

Thetotalinternalarchitectureof8086microprocessorcanbebasicallydividedintotwodifferent units.

- 1.BusInterfacesUnit(BIU)

- 2.Execution Unit (EU)

### 1. BusInterfacesUnit(BIU):

- Itisresponsiblefortransferofdataandaddressbetweentheprocessor,memoryand input output device.

- It receives the data from the IO device and stored the data in a 6 bytes instruction queues in FIFO sequence and this data is transferred to the execution unit for arithmetic and logical operation.

- Thefunction of different units of businterface unitare

## **6bytesinstructionqueue**

- o Itsfunctionistoreceive6no.of8bitdataatatimeandstoresthedatainitand then this data can be transferred to execution unit for performing arithmetic and logical operation i.e. execution operation.

- The data is received from IO device to the 6 bytes instruction queue in FIFO sequence.

### Segmentregister

- Thereare4segmentregister

- Code segment register (CS): It basically used to store the opcode of aninstruction.

- <u>Data segment register (DS):</u> It basically used to store the operand of an instruction.

- Extra segment register (ES): It is basically used to store the character or string instruction such as consonant, vowel, character etc.

- Stacksegmentregister(SS):Stackisasetofmemorylocationwhose address is different from main memory address.

- ✓ We can transfer the data from main memory to stack memory by pushinstructionandwecanreceivethedatafromstackmemoryto main memory by pop instruction. So, segment register is basically used to store the stack memory value.

- ✓ To locate a particular memory address, we take the help of stack pointer and given by the commandLXI SP 9605<sub>H</sub>.

# Instructionpointer(IP)

Itsfunctionissameasthat ofprogram counterof8085microprocessorand is basicallyused tocheckwhethertheaddressfornext instructionisavailableor not. So, it stores the OFF-SET address.

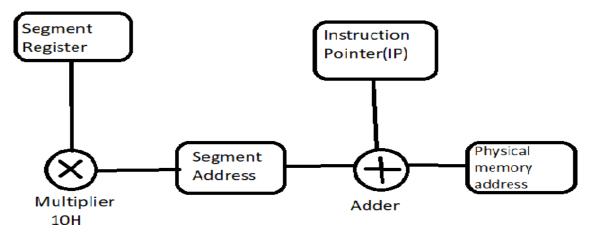

# **Buscontroland addressgeneration**

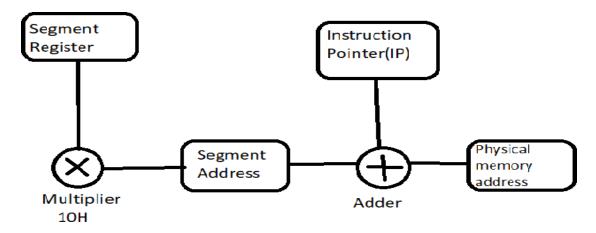

- o It is basically used to generate 20 bits effective memory address or physical memory address.

- One address is generated from the segment register which is of 16 bit and when the address goes to the bus control and address generation it gets multiplied by the multiplier circuit of value 10<sub>H</sub>. So, at the output we get a segment address of 20 bit.

- Another address is generated from the instruction pointer which is of 16 bit and is known as OFF-SET address or assembly line address.

- So, whenthis address goes to the bus control and address generation, it gets added of with the help of adder circuit which is present inside the bus control and address generation.

- Hencethe 20-bitsegmentaddressisaddedupwiththe16-bitIPaddresswith the help of adder circuit and at the output we get a 20-bit effective memory address or physical memory address.

- Effectivememoryaddress(EMA)orPhysical memoryaddress(PMA)=Segment address\*10<sub>H</sub> +Instruction pointer

- $\circ \quad The block diagram of physical address generation is shown as follows. \\$

[Blockdiagramofphysical address generations]

# 2. ExecutionUnit(EU):

- The execution unit receives the opcode of an instruction from the 6 byte instruction queue decodes it and perform the arithmetic and logical operation and stores the result.

- Thefunctionofdifferentunitsofexecutionunitsare

#### **ALU**

- o It is basically used to perform the arithmetic and logical operation such as addition, subtraction, multiplication, division, increment, decrement, comparison.

- Afterthearithmeticandlogicaloperation, the result is check by the status flag.

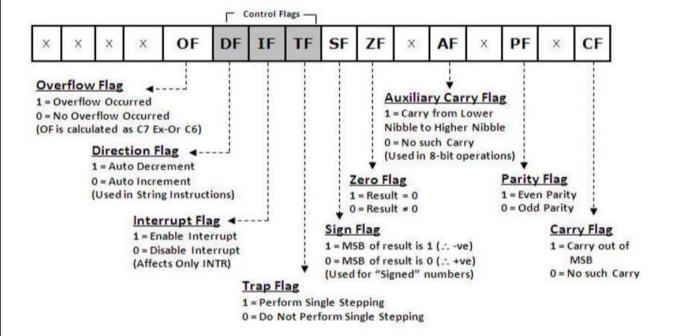

### StatusFlag

- Thestatusflagsarebasicallyusedtocheckwhethertheresultiswritingorwrong.

- Accordingly,in8086microprocessorthereare9activestatusflagsoutofwhich6are conditional flag and 3 are control flag.

- **Conditionalflag:**Conditionalflagsarethosewheretheoutputdependsuponthe input.TheconditionalflagsareSignflag,zeroflag,Auxiliaryflag,Parityflag,Carry flag and overflow flag.

- ➤ **Sineflag:**Afterthearithmeticoperationiftheresultisnegativethensign flag is tends to logic 1 otherwise it will tend to logic 0.

- ➤ **Zeroflag:**Afterthearithmeticoperationiftheresultiszerothenzeroflag will tend to logic 1 otherwise it will tend to logic 0.

- ➤ **Auxiliaryflag:**Afterthearithmeticoperationifthereisacarryfrom3<sup>rd</sup>to 4<sup>th</sup>bitthenauxiliarycarrywilltendstologic1otherwiseitwilltendtologic 0.

- ➤ **Parityflag:**Afterthearithmeticoperationiftheresultofthesumcontains evenno. of1'sthenparityflagwilltendtologic1otherwiseitwilltendto logic 0.

- ➤ **Carry flag:** After the arithmetic operation if the result is more than 8 bit thentherewillbeacarryfrom7-8bitsocarryflagwilltendstologic1and incaseof16bitoperationifthereisacarryfrom15to16bitthecarryflag will tends to logic 1 otherwise it will tends to logic 0.

- ➤ **Overflowflag:**Afterthearithmeticoperationiftheresultismorethan16 bits,in that case the data cannot be stored in accumulator or destination register.So,inthatcasetheoverflowflagwilltendstologic1otherwiseit will tend to logic 0.

So, inconditional flagthe output is depends on the input

- **+Controlflag:**Thecontrolflagsarebasicallyusedforcontrol-orientedactivitysuch as to stop the program, set or reset the operation, status flag manipulation, interruptoperation.So,inthiscaseitisusedforcontrol-orientedactivityandhere theoutputisdoesnotdependsuponinput. ThecontrolflagsareDirectionalflag, Interrupt flag, Trap flag.

- ➤ **Directionalflag:**Incaseofcharacterorstringoperationinthatcasethe directional flag will tends logic 1 otherwise it will tend to logic 0.

- ➤ Interrupt flag and Trap flag: These two flags are basically used as interrupt operation.

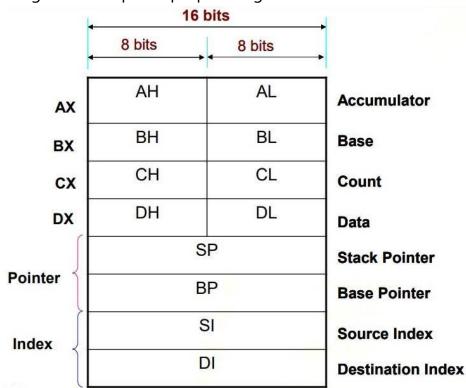

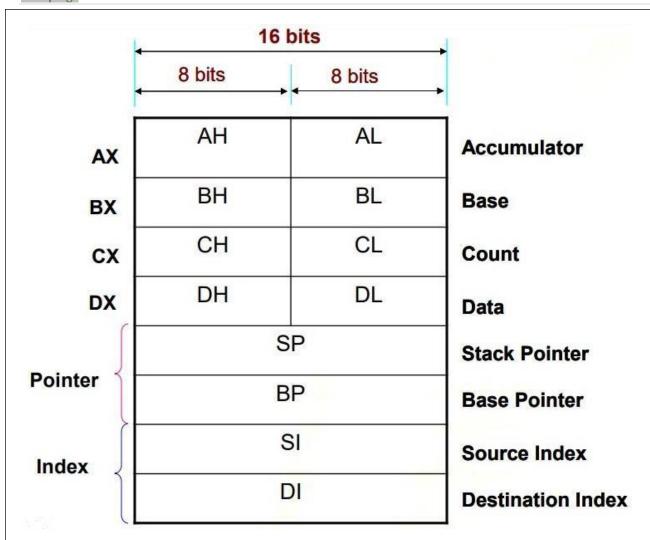

#### Resistors

There are two types of register in 8086 microprocessor such as Generalpurposeregister and Special purpose register.

**4General-purpose register:** The general-purpose register are  $A_H$  and  $A_L$  i.e. A higher order and A lower order. Similarly,  $B_H$  and  $B_L$ ,  $C_H$  and  $C_L$ ,  $D_H$  and  $D_L$  respectively. Each register can store individually 8 bit of data and combine form it can store 16 bit of data so,

$A_H + A_L = A_X(16bit) B_H$   $+ B_L = B_{X(16bit)} C_H$   $+ C_L = C_{X(16bit)}$   $D_H + D_L = D_{X(16bit)}$

e.g.**mov AH,08**<sub>H</sub>-Moveimmediatelythedata08toA<sub>H</sub>register.

MOVAL,08<sub>H</sub>-Moveimmediatelythedata08toA<sub>L</sub> register.

*MOVAX*, 1264<sub>H</sub>-Movethe16-bitdata1264HtoA<sub>x</sub>register.

- Since these registers are commonly used for storing the data temporarily for any arithmetic and logical operation so these are known as general-purpose register.

- **↓Special purpose register:** The special purpose registers are Stack pointer (SP), Base pointer (BI), Source index register (SI), Destination index register (DI). These are known as special purpose register because they are used for some specific operation and these are 16-bit registers.

- > Stack pointer (SP): Through stack pointer we can locate to a particular stack pointer address e.g. LXI SP, 9505н.

- ➤ Base pointer (BP): It is basically use to store the OFF-SET address (value of instruction pointer address).

- > **Sourceindexregister(SI):**Itisbasicallyusedtostorethestringaddress e.g.*Movsi,[2000<sub>H</sub>]*-MovetheOFF-SET address2000<sub>H</sub>toSI register.

- ➤ **Destination index register (DI):** It is basically used to store the end address e.g. **MOV DI**, [2005<sub>H</sub>]-Move immediately the OFF-SET address 2005<sub>H</sub> to DI register.

## INSTRUCTIONSETSOF8086MICROPROCESSORS

Instructions are sets of commands given to the processor to perform a specific operation accordinglyin8086microprocessorthetotalinstructionsetcanbedividedinto8differenttypes according to type of operation it performs. The instructions are;

- 1. Datatransforminstruction

- 2. Arithmeticinstruction

- 3. Logicalinstruction

- 4. Branchcontrolinstruction

- 5. Iterationcontrolinstruction

- 6. Interruptinstruction

- 7. Processorcontrol

- 8. Stringinstruction

- Datatransforminstruction: Itisbasically used for transferring the data from one register to another register or register to memory without changing the content. E.g. MOVAX, BX-Movethecontent of BX register to AX register. MOV AX, 1234<sub>H</sub>-Move the 16-bit data 1234<sub>H</sub> to A<sub>X</sub> register.

- **2. Arithmeticinstruction:** These are basically used for arithmetic operation such as addition, subtraction, multiplication, division, increment, decrement etc. In this case the final result may change.

- **3. Logical instruction:** These instructions are basically used for logical operation such as ANA (AND), ORA (OR), XRA (XOR), CMP (COMPARE) etc.

- **4. Branch control instruction:** The instruction under this group are basically used for conditional or unconditional jump operation.

E.g.

- JNZ- Jump if the counter data in the register C is not zero to label loop.

JNC- Jump if there is no carry or borrow to label loop.

- **5. Iterationcontrolinstruction:** Theseinstructions are basically used in label portion for loop operation.

- E.g.LOOP,CALL,AHEAD,STOP.

- **6. Interrupt instruction :** The instruction under this group are basically used for interrupt operation that means to stop the current program and jump to some other program which is required at the specific moment of time and after the completion of that specific program the processor can again return back to the original program and these are given by through certains of tware instruction such as INT, INT<sub>0</sub>, INT<sub>1</sub>, INT<sub>2</sub>, INTR.

**7. Processor control:** The instruction under this group are basically used for status flag manipulation and for machine control operation.

E.g.CLC-Clearthecarry bit.

CLD-Clearthedirectional flag.

STC-Setthecarry bittologic1.

STD-Setthedirectionaltologic1.

CMC-Complementofcarrybit.

**HALT**

**PUSH**

POP

**8. Stringinstruction:** Stringisaseries of bytes or series of words to redinase quential memory location.

In 8085 microprocessor there are certain instructions which are basically used to move or store a string of data bytes.

E.g. MOVS-Movethestring(singlebit). MOV

SP- Move the string of data bytes. CMP S-

Comparison of string.

CMPSP-Comparisonofstringofdatabytes.

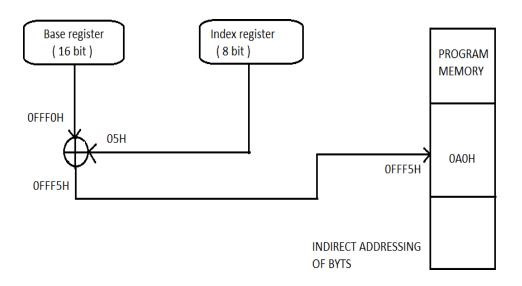

# ADDRESSINGMODEOF8086MICROPROCESSOR

Itisthetechniquethroughwhichwearespecifyingdataforoperationorhowtheoperand data is specified accordingly in 8086 microprocessors. There are 8 different addressing mode according to the type of operation it performs.

- 1. Registeraddressingmode

- 2. Immediateaddressing mode

- 3. Directaddressingmode

- 4. Registerindirectaddressingmode

- 5. Baseaddressingmode

- 6. Indexaddressingmode

- 7. Baseindexaddressing mode

- 8. Baseindexand displacement

- 1. **Register addressing mode:**In this type ofaddressingmode the operanddata is not directly specified in the instruction itself but it is specified by some register.

E.g.MOV AX,BX-MovethecontentofBXregistertoAX register.

MOVAH,AL-Movethecontent of Alregister to Alregister.

2. **Immediateaddressingmode:**Inthistypeofaddressingmodetheoperanddatais directly specified in the instruction itself.

E.g.MOV AH,08H- Moveimmediatelythedata08HtoAH register.

MOVAX, 1264<sub>H</sub>-Movethe16-bit data1264<sub>H</sub>toAX register.

**3. Directaddressingmode:**Indirectaddressingmodetheoperandaddressisdirectly specified in the instruction itself.

E.g.

MOVAX,[9000H]-Movethecontent of memory address 9000H to AX register.

*MOVBX,[9001<sub>H</sub>]*-Movethecontentof memoryaddress9001<sub>H</sub>toBXregister.

4. **Register indirect addressing mode:** In this typeof addressing modethe operand data is not directly transferred to the accumulator; at first it stored in some memory address and the transferred to the accumulator.

E.g.*MOVBX*,[9001] *MOV*

AX, BX

5. **Base addressing mode:** In this type of addressing mode the operand address is one of thecontentsofbasepointerorstackpointer.Basically,itstorestheOFF-SETvalueofthe instruction pointer.

E.g.  $MOV\ BX$ , [9005<sub>H</sub>]- Move the content of the memory address 9005<sub>H</sub> to BX register base pointer.

6. **Index addressing mode:** It is basically used to store the string address or the end address. The source index register is used to store the starting address and destination index register is used to store the end address.

E.g.

MOVSI,[9000<sub>H</sub>]-Movethecontentofmemoryaddress9000<sub>H</sub>totheSlregister.

MOVDI,[9005<sub>H</sub>]-Movethecontentofmemoryaddress9000<sub>H</sub>to DI register.

7. **Baseindexaddressingmode:**InthismodetheoperandOFF-SETisthesumofthe content of base register or BX and index register SI or DI.

E.g.

MOVAX,[BX+SI]-Movethecontentofbasepointerorstackpointerandthe source index value to AX register or accumulator.

MOV AX,[BX+DI]- Move the sum of the content of base register and destination index register value to accumulator.

8. **Baseindexanddisplacement:**InthisaddressingmodetheoperandOFF-SETisthesum of the content off base pointer + SI or DI + 8-bit or 16-bit displacement value.

E.g.MOVAX,[ $AX+SI+08_H$ ]

# PROGRAMIN8086 MICROPROCESSORS

# Programtofindlargestno.ofdata array:-

| LABEL              | MNEMONICS<br>MOV   | opera<br>AX, 00    |                                                | COMMENT Movethe16-bitdata0000Hto                              |  |  |  |

|--------------------|--------------------|--------------------|------------------------------------------------|---------------------------------------------------------------|--|--|--|

|                    |                    |                    |                                                | accumulator or AX register.                                   |  |  |  |

|                    | MOV                | SI, [74            | [00]                                           | Movethecontentofthememory                                     |  |  |  |

|                    | MOV                | CX,SI              |                                                | address 7400H to SI register.  MovethecontentofSIregistertoCX |  |  |  |

|                    | IVIOV              | CA,51              |                                                | registerwhichisbasicallyusedto store                          |  |  |  |

|                    |                    |                    |                                                | the counter data.                                             |  |  |  |

| BACK               | INC                | SI                 |                                                | Incrementthecontent of source                                 |  |  |  |

|                    |                    |                    |                                                | indexregisterbynextbittoprovide thenextcounterdata.           |  |  |  |

|                    | INC                | SI                 |                                                | Increment the content of the source                           |  |  |  |

|                    | IIVC               | Ji                 |                                                | index address by next bit to provide                          |  |  |  |

|                    |                    |                    |                                                | the next value.                                               |  |  |  |

|                    | CMP                | AX, (S             | l)                                             | Compare the content of AX register                            |  |  |  |

|                    |                    |                    |                                                | withSIregisterwhereAXactsas                                   |  |  |  |

|                    |                    |                    |                                                | accumulator in 8086                                           |  |  |  |

|                    | JA                 | NEXT               |                                                | microprocessors.  Jumpiftheno.inAXregisteris                  |  |  |  |

|                    | 37.1               | TTEXT              |                                                | greaterthan Slregistertolevelnext.                            |  |  |  |

|                    | MOV                | AX, (S             | l)                                             | MovethecontentofSIregistertoAX                                |  |  |  |

|                    |                    |                    |                                                | register.                                                     |  |  |  |

| NEXT               | LOOP               | BACK               |                                                | Go to the label back till the counter                         |  |  |  |

|                    |                    |                    |                                                | datainSlregisterasreachthe                                    |  |  |  |

|                    | MOV                | (7565)             | ) ΔΧ                                           | highestvalue.  Move the content of AX resistor to             |  |  |  |

|                    | 1410 4             | (1303)             | ), <b>,                                   </b> | memory address resister tomemory                              |  |  |  |

|                    |                    |                    |                                                | address.                                                      |  |  |  |

|                    | INT<br>END         | 2F                 |                                                |                                                               |  |  |  |

| DATA:              |                    |                    |                                                |                                                               |  |  |  |

| 7400-05            | 7403-83            | 7406-39            | 7409-84                                        |                                                               |  |  |  |

| 7401-00<br>7402-41 | 7404-58<br>7405-72 | 7407-46<br>7408-53 | 740A-30<br>740B-96                             |                                                               |  |  |  |

| 1402-41            | 1403-12            | 1400-33            | 140D-90                                        |                                                               |  |  |  |

# $\underline{Program to find smallest no. from a data array:} \\$

| LABEL              | MNEMONICS          | OPERAND    | COMMENTS                                                                                  |

|--------------------|--------------------|------------|-------------------------------------------------------------------------------------------|

|                    | MOV                | AX,FFFF    | Movethehighestvalue $FFFF_H$ toAX register.                                               |

|                    | MOV                | SI, [7400] | Move the content of memory address 7400 <sub>H</sub> to SI register.                      |

|                    | MOV                | CX, (SI)   | Move the content of SI register to CXregisterwhichisbasicallyused forcounteroperation.    |

| BACK               | INC                | SI         | IncrementthecontentofSIbynext bit to provide the next counter data.                       |

|                    | INC                | SI         | Increment the content of Sladdress by next bit to provide the next data.                  |

|                    | CMP                | AX, (SI)   | ComparethecontentofAXregister with the SI register.                                       |

|                    | JB                 | NEXT       | Jumpwithborrowandcarry.                                                                   |

|                    | MOV                | AX, (SI)   | Move the content of SI register to AX register.                                           |

| NEXT               | LOOP               | BACK       | Gotothelabelbacktillthecounter dataofSIregisterorCXregisterhas reach the highest value.   |

|                    | MOV                | (7565),AX  | MovethecontentofAXregisterto the memory address 7565 <sub>H</sub> and 7566 <sub>H</sub> . |

|                    | END                |            |                                                                                           |

| DATA:              |                    |            |                                                                                           |

| 7400-05            | 7406-39            | 7565-39    | RESULTAX=4639                                                                             |

| 7401-00            | 7407-46            | 7566-46    |                                                                                           |

| 7402-41            | 7408-53            |            |                                                                                           |

| 7403-83<br>7404-58 | 7409-84<br>740A-30 |            |                                                                                           |

| 7404-36<br>7405-72 | 740A-30<br>740B-96 |            |                                                                                           |

|                    |                    |            |                                                                                           |

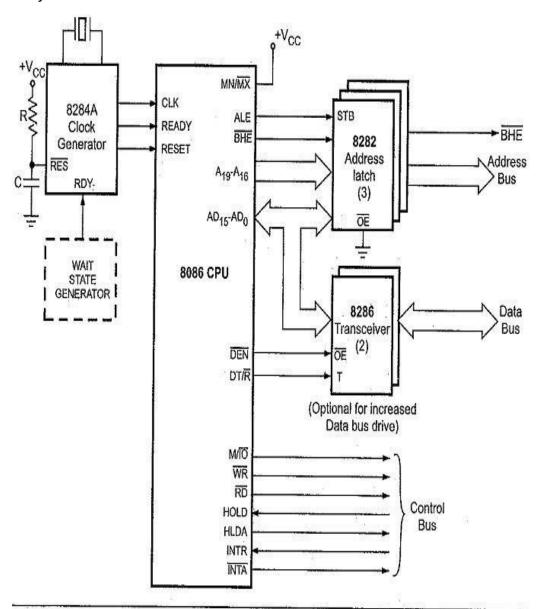

### MINIMUMMODECONFIGURATIONOF8086MICROPROCESSOR

Whenthe single processor is used, thenthe 8086 microprocessor operates in minimum mode MN/MX' tends to logic 1 i.e. MN=1, MX'=1, MX=0

So, for simple input output operation or when a single processor is used then the 8086 microprocessor operates in minimum mode and in that case the control signal pins which are attachtominimummodegetactivated. The control signal pins are RD', WR', ALE, IO/M', HOLD, HLDA, DEN'.

The different units which are attached to the minimum mode control pin to perform different memory read and IO read, IO write operation is known as minimum mode configuration.

Thedifferentunitsare:

#### i. Latches:

- Thereare2to3latchesarepresentandtheselatchesareoctalinnaturethatmeans each latchcan stores8 bitsofdatasothe twolatches canstore16 bitofdata and 3 latches can stores 20 bits of address.

- Latchesaretemporarystoragedeviceor flipflop

- The ALE signal is connected to the latches and its function is to separate the address from address and data bus.

- The bus high enable pin is also attach to the latches and its main function is to check the validity of address and the address and data line are also attached to latches.

#### ii. Transreceiver:

- Transreceivermeanstransferandreception of data.

- Through the trans receiver we can transfer the data from the processor to the IO device and in that case the DT/R' tends to logic 1 i.e. DT=1, R'=1, R=0.

- IfDT/R'tendstologic0thenDT=0,R'=0,R=1soreadoperationisperformi.e.data is received from the IO device to processor.

- Data enable pin is also attached to the trans receiver and its main function is tocheck the validity of the data.

#### iii. RAM:

- Itisknownasrandomaccess memory.

- Itstemporarystoresthedataanditvolatileinnaturethatmeansifthepower supply OFF the data gets deleted.

- Herawecanperformbothread and writeoperation.

#### iv. EPROM:

- EPROM-ErasableProgrammableReadOnlyMemory.

- Itisnon-volatileinnature andisusedtostoresthelibraryfunction.

- Itisonlyusedforreadoperation.

## v. IOdeviceorperipheraldevice:

- Itisbasicallyusedforprovidinginputdatatotheprocessor.

- In minimum modesingle processorisusedsoasingle IOdevice isconnectedto processor.

### vi. Clockgenerator:

- It is basically used for providing input clock frequency to the processor so that we can check how much time the processor will take to execute an operation.

- Itcanvaryfrom5MHz to10MHz.

Fig. 10.2 Typical minimum mode configuration

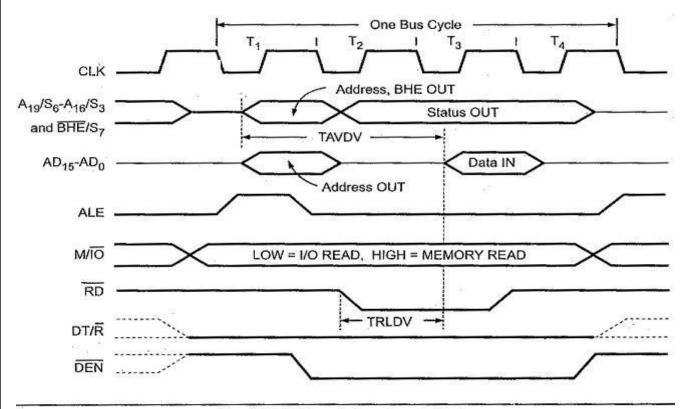

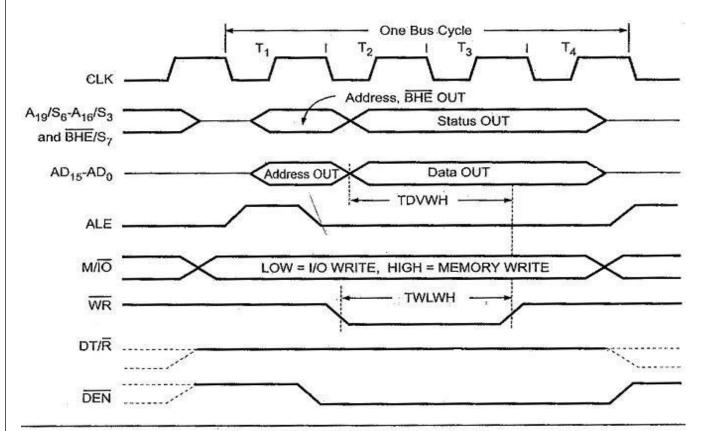

# Timing diagram of minimum mode operation of 8086 microprocessor:

Fig. 10.7 (a) Input (read operation)

Fig. 10.7 (b) Output (write operation)

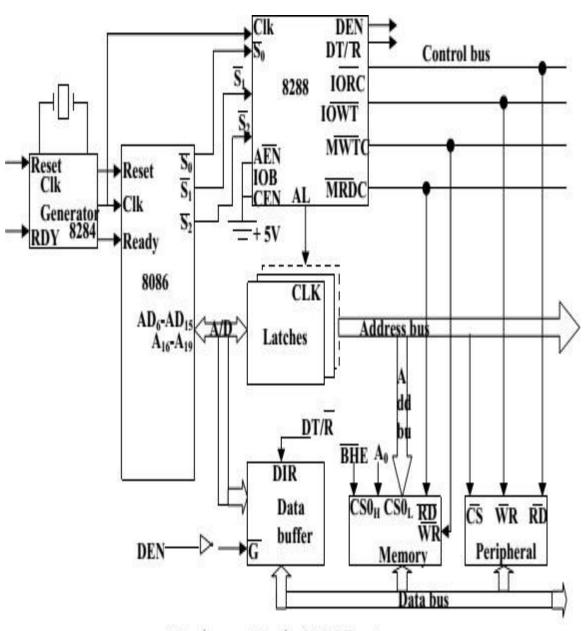

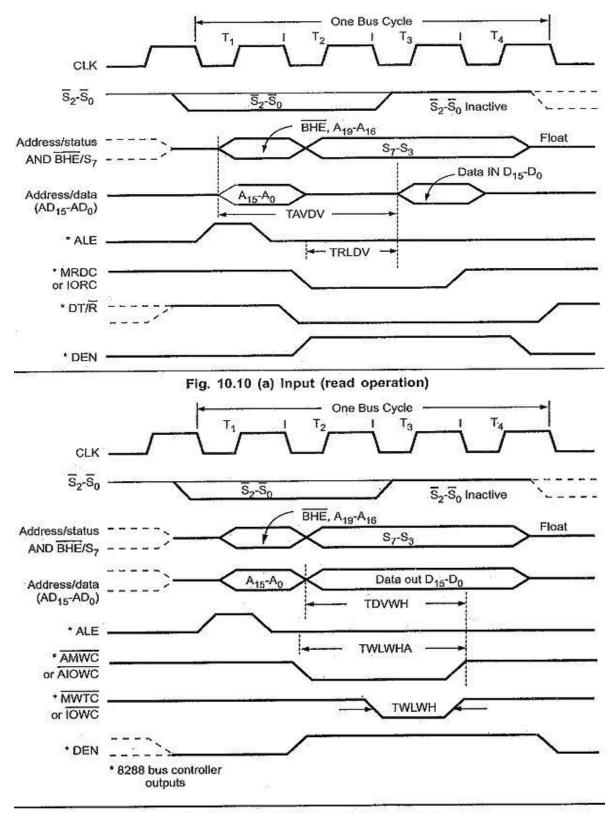

### MAXIMUMMODECONFIGURATIONOF8086MICROPROCESSOR

Formultipurposeoperation the 8086microprocessors can operatesin maximum mode and in that case the MN/MX' pin tends to logic 0 i.e. MN=0, MX'=0, MX=1.

InmaximummodeoperationmultipleRAM,multipleROM,multipleIOdevicesareattachedto the processor to perform different memory read and memory write and IO read and IO write operation.