#### 5th Semester

## **Advanced Computer Architecture**

## **Objectives**

- To understand the advance hardware and software issues of computer architecture

- To understand the multi-processor architecture & connection mechanism

- To understand multi-processor memory management

## Module-I: (10 Hours)

Microprocessor and Microcontroller, RISC and CISC architectures, Parallelism, Pipelining fundamentals, Arithmetic and Instruction pipelining, Pipeline Hazards, Superscalar Architecture, Super Pipelined Architecture, VLIW Architecture, SPARC and ARM processors.

#### Module-II: (10 Hours)

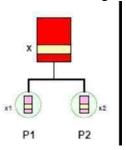

Basic Multiprocessor Architecture: Flynn's Classification, UMA, NUMA, Distributed Memory Architecture, Array Processor, Vector Processors.

### **Module-III: (10 Hours)**

Interconnection Networks: Static Networks, Network Topologies, Dynamic Networks, Cloud computing.

## **Module IV (10 Hours)**

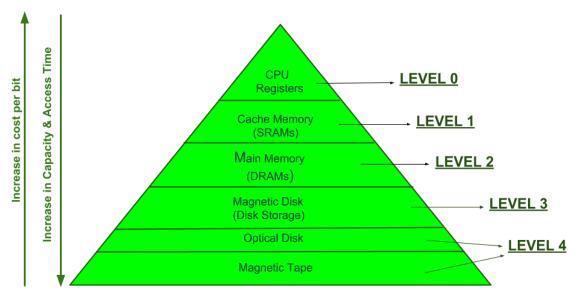

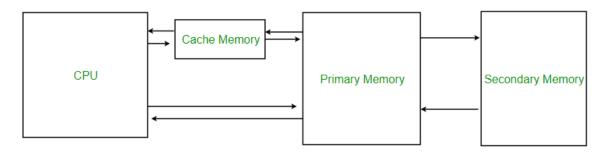

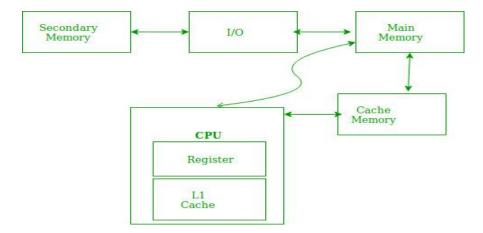

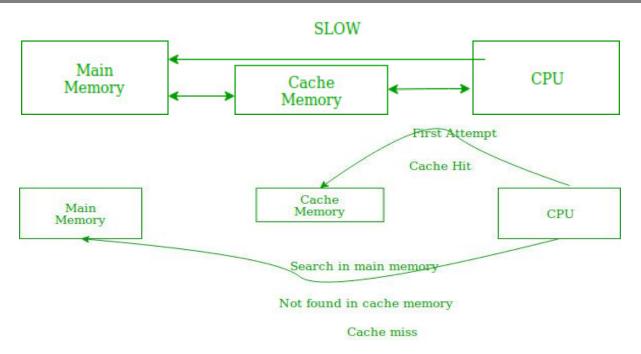

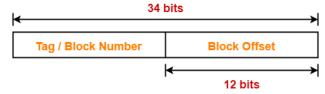

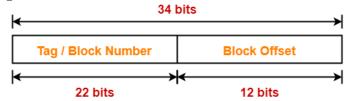

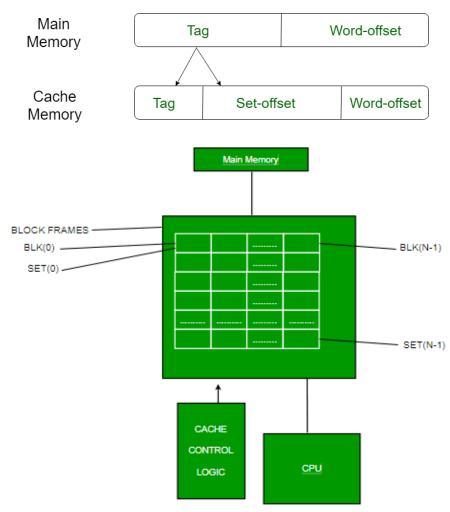

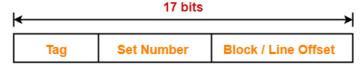

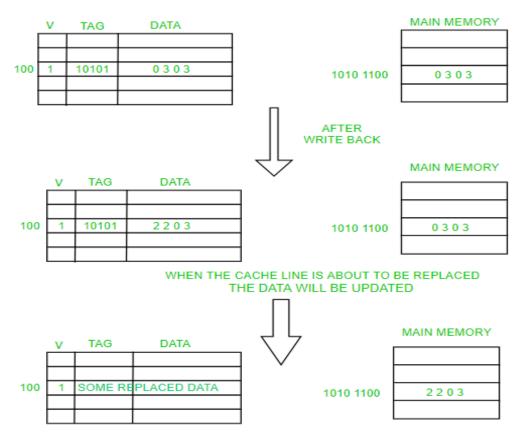

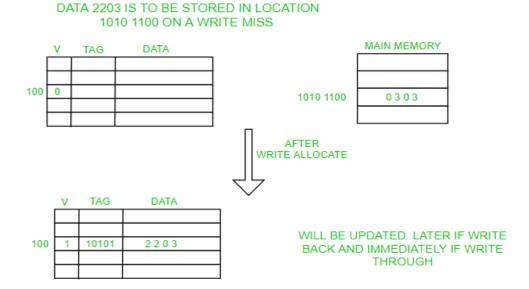

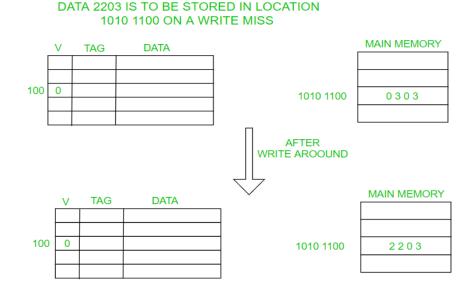

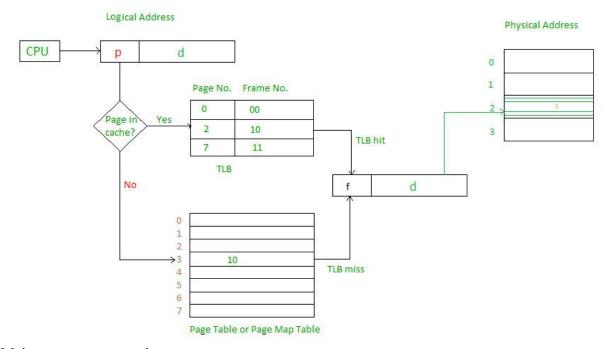

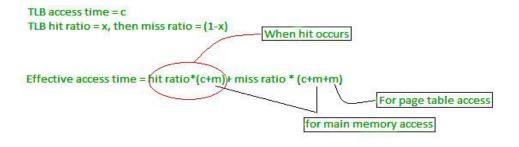

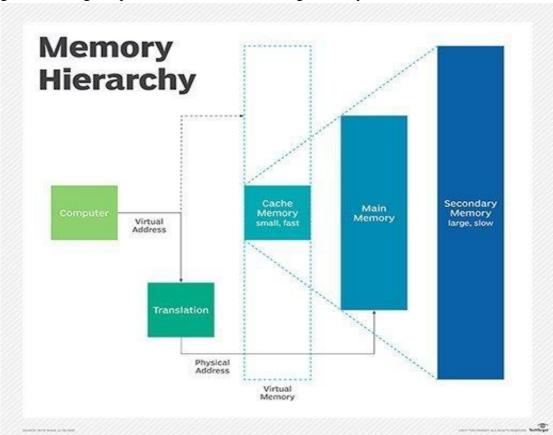

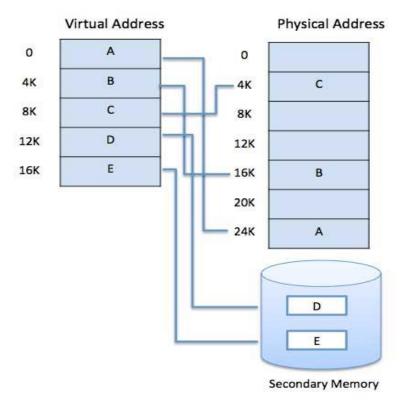

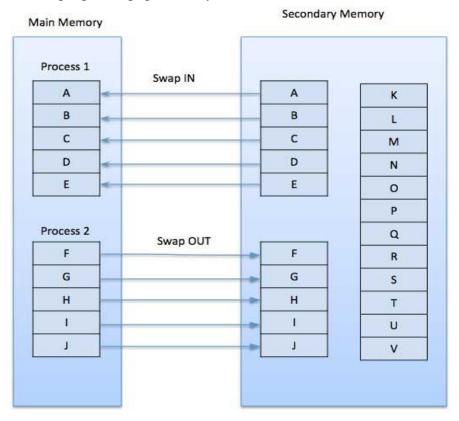

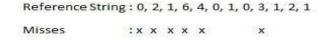

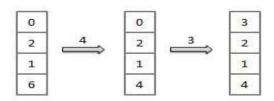

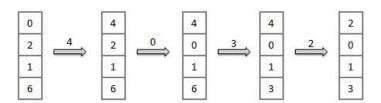

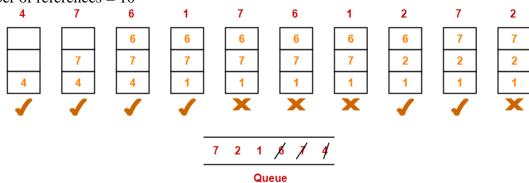

Memory Technology: Cache, Cache memory mapping policies, Cache updating schemes, Virtual memory, Page replacement techniques, I/O subsystems.

#### **Outcomes**

- Ability to analyze the abstraction of various advanced architecture of a computer

- Ability to analyze the multi-processor architecture & connection mechanism

- Ability to work out the tradeoffs involved in designing a modern computer system

#### **Books:**

- [1] John L. Hennessy and David A. Patterson, Computer Architecture: A Quantitative Approach, Morgan Kaufmann, 6th edition, 2017

- [2] Carl Hamacher, Zvonko Vranesic, Safwat Zaky, Computer Organization, McGraw Hill, 5th Ed, 2014

- [3] Kai Hwang, Advanced Computer Architecture: Parallelism, Scalability, Programmability, McGraw-Hill, 3rd Ed, 2015

## **Digital Learning Resources:**

Course Name: Advanced Computer Architecture

Course Link: https://nptel.ac.in/courses/106/103/106103206/

Course Instructor: Prof.John Jose, IIT, Guwahati

Course Name: High Performance Computer Architecture Course Link: https://nptel.ac.in/courses/106/105/106105033/

Course Instructor: Prof.A. Pal, IIT, Kharagpur

# **Introduction to microprocessor and microcontroller**

- A microprocessor is an IC which has only the CPU inside them, i.e. only the processing powers such as Intel's Pentium 1,2,3,4, core 2 duo, i3, i5 etc. These microprocessors don't have RAM, ROM, and other peripherals on the chip. A system designer has to add them externally to make them functional.

- Applications of microprocessor include Desktop PC's, Laptops, notepads etc.

- A microcontroller has a CPU, in addition with a fixed amount of RAM, ROM and other peripherals all embedded on a single chip. At times it is also termed as a mini computer or a computer on a single chip. Today different manufacturers produce microcontrollers with a wide range of features available in different versions. Some manufacturers are ATMEL, Microchip, TI, Freescale, Philips, Motorola etc.

- Microcontrollers are designed to perform specific tasks. Specific means applications where the

relationship of input and output is defined. Depending on the input, some processing needs to be

done and output is delivered.

- For example, keyboards, mouse, washing machine, digicam, pendrive, remote, microwave, cars, bikes, telephone, mobiles, watches, etc. Since the applications are very specific, they need small resources like RAM, ROM, I/O ports etc and hence can be embedded on a single chip. This in turn reduces the size and the cost.

- Microprocessors find applications where tasks are unspecific like developing software, games, websites, photo editing, creating documents etc. In such cases the relationship between input and output is not defined. They need high amount of resources like RAM, ROM, I/O ports etc.

- The clock speed of the Microprocessor is quite high as compared to the microcontroller. Whereas the microcontrollers operate from a few MHz to 30 to 50 MHz, today's microprocessors operate above 1GHz as they perform complex tasks.

- Generally, a microcontroller is far cheaper than a microprocessor. However, a microcontroller cannot be used in place of microprocessor and using a microprocessor is not advised in place of a microcontroller as it makes the application quite costly.

- A microprocessor cannot be used stand alone. They need other peripherals like RAM, ROM, buffer, I/O ports etc and hence a system designed around a microprocessor is quite costly.

# **Evolution of Microprocessors**

- Transistor was invented in 1948 (23 December 1947 in Bell lab).

- IC was invented in 1958 (Fair Child Semiconductors) By Texas Instruments J kilby.

- First microprocessor was invented by INTEL (INTegrated ELectronics).

**Size of microprocessor** – 4 bit

|           |                      |             | Number Of   |               |

|-----------|----------------------|-------------|-------------|---------------|

| Name      | Year Of Invention    | Clock Speed | Transistors | Inst. Per Sec |

| INTEL     | 1971 by Ted Hoff and |             |             |               |

| 4004/4040 | Stanley Mazor        | 740 KHz     | 2300        | 60,000        |

Size of microprocessor – 8 bit

| Name | Year Of Invention         | Clock<br>Speed | Number Of<br>Transistors | Inst. Per Sec             |

|------|---------------------------|----------------|--------------------------|---------------------------|

| 8008 | 1972                      | 500 KHz        |                          | 50,000                    |

| 8080 | 1974                      | 2 MHz          | 60,000                   | 10 times faster than 8008 |

| 8085 | 1976 (16 bit address bus) | 3 MHz          | 6500                     | 769230                    |

Size of microprocessor – 16 bit

|        | -                                       | 1           | l           | 1         |

|--------|-----------------------------------------|-------------|-------------|-----------|

|        |                                         |             | Number Of   | Inst. Per |

| Name   | Year Of Invention                       | Clock Speed | Transistors | Sec       |

|        | 1978 (multiply and divide instruction,  | 4.77 MHz,   |             | 2.5       |

| 8086   | 16 bit data bus and 20 bit address bus) | 8MHz, 10MHz | 29000       | Million   |

|        | 1979 (cheaper version of 8086 and 8 bit |             |             | 2.5       |

| 8088   | external bus)                           |             |             | Million   |

|        | 1982 (80188 cheaper version of 80186,   |             |             |           |

|        | and addtional components like interuppt |             |             |           |

| 80186/ | controller, clock generator, local bus  |             |             |           |

| 80188  | controller,counters)                    | 6 MHz       |             |           |

|        | 1982 (data bus 16bit and address bus 24 |             |             |           |

| 80286  | bit)                                    | 8 MHz       | 134000      | 4 Million |

**Size of microprocessor** – 32 bit

|         |                                  | Clock    | Number Of          |                      |

|---------|----------------------------------|----------|--------------------|----------------------|

| Name    | Year Of Invention                | Speed    | <b>Transistors</b> | Inst. Per Sec        |

|         | 1986 (other versions 80386DX,    |          |                    |                      |

| INTEL   | 80386SX, 80386SL and data bus 32 | 16 MHz – |                    |                      |

| 80386   | bit address bus 32 bit)          | 33 MHz   | 275000             |                      |

| INTEL   | 1986 (other versions 80486DX,    | 16 MHz – | 1.2 Million        | 8 KB of cache        |

| 80486   | 80486SX, 80486DX2, 80486DX4)     | 100 MHz  | transistors        | memory               |

|         |                                  |          |                    | Cache memory 8       |

|         |                                  |          |                    | bit for instructions |

| PENTIUM | 1993                             | 66 MHz   |                    | 8 bit for data       |

Size of microprocessor – 64 bit

| Name       | Year Of Invention          | Clock Speed       | Number Of   | Inst. Per Sec  |

|------------|----------------------------|-------------------|-------------|----------------|

| ranic      | 2006 (other versions core2 | Сюск бреси        | Transistors | 64 KB of L1    |

| INTEL      | duo, core2 quad, core2     |                   | 291 Million |                |

| core 2     | extreme)                   | 1.2 GHz to 3 GHz  | transistors | MB of L2 cache |

|            |                            | 2.2GHz - 3.3GHz,  |             |                |

|            |                            | 2.4GHz – 3.6GHz,  |             |                |

| i3, i5, i7 | 2007, 2009, 2010           | 2.93GHz – 3.33GHz |             |                |

### **Generations of microprocessor:**

**First generation:** From 1971 to 1972 the era of the first generation came which brought microprocessors like INTEL 4004 Rockwell international PPS-4 INTEL 8008 etc.

**Second generation:** The second generation marked the development of 8 bit microprocessors from 1973 to 1978. Processors like INTEL 8085 Motorola 6800 and 6801 etc came into existence.

**Third generation:** The third generation brought forward the 16 bit processors like INTEL 8086/80186/80286 Motorola 68000 68010 etc. From 1979 to 1980 this generation used the HMOS technology.

**Fourth generation:** The fourth generation came into existence from 1981 to 1995. The 32 bit processors using HMOS fabrication came into existence. INTEL 80386 and Mororola 68020 are some of the popular processors of this generation.

**Fifth generation:** From 1995 till now we are in the fifth generation. 64 bit processors like PENTIUM, celeron, dual, quad and octa core processors came into existence.

## Types of microprocessors:

**Complex instruction set microprocessor:** The processors are designed to minimise the number of instructions per program and ignore the number of cycles per instructions. The compiler is used to translate a high-level language to assembly level language because the length of code is relatively short and an extra RAM is used to store the instructions. These processors can do tasks like downloading, uploading and recalling data from memory. Apart from these tasks these microprocessors can perform complex mathematical calculation in a single command.

Example: IBM 370/168, VAX 11/780

**Reduced instruction set microprocessor:** These processor are made according to function. They are designed to reduce the execution time by using the simplified instruction set. They can carry out small things in specific commands. These processors complete commands at faster rate. They require only one clock cycle to implement a result at uniform execution time. There are number of registers and less number of transistors. To access the memory location LOAD and STORE instructions are used.

Example: Power PC 601, 604, 615, 620

**Super scalar microprocessor:** These processors can perform many tasks at a time. They can be used for ALUs and multiplier like array. They have multiple operation unit and perform many tasks, executing multiple commands.

**Application specific integrated circuit:** These processors are application specific like for personal digital assistant computers. They are designed according to proper specification.

**Digital signal multiprocessor:** These processors are used to convert signals like analog to digital or digital to analog. The chips of these processors are used in many devices such as RADAR SONAR home theatres etc.

## Advantages of microprocessor -

- High processing speed

- Compact size

- Easy maintenance

- Can perform complex mathematics

- Flexible

- Can be improved according to requirement

## Disadvantages of microprocessors -

- Overheating occurs due to overuse

- Performance depends on size of data

- Large board size than microcontrollers

- Most microprocessors do not support floating point operations

# **Pipelining**

To improve the performance of a CPU we have two options:

- 1) Improve the hardware by introducing faster circuits.

- 2) Arrange the hardware such that more than one operation can be performed at the same time.

Since, there is a limit on the speed of hardware and the cost of faster circuits is quite high, we have to adopt the  $2^{nd}$  option.

**Pipelining:** Pipelining is a process of arrangement of hardware elements of the CPU such that its overall performance is increased. Simultaneous execution of more than one instruction takes place in a pipelined processor.

Example: Consider a water bottle packaging plant. Let there be 3 stages that a bottle should pass through, Inserting the bottle(**I**), Filling water in the bottle(**F**), and Sealing the bottle(**S**). Let us consider these stages as stage 1, stage 2 and stage 3 respectively. Let each stage take 1 minute to complete its operation.

Now, in a non-pipelined operation, a bottle is first inserted in the plant, after 1 minute it is moved to stage 2 where water is filled. Now, in stage 1 nothing is happening. Similarly, when the bottle moves to stage 3, both stage 1 and stage 2 are idle. But in pipelined operation, when the bottle is in stage 2, another bottle can be loaded at stage 1. Similarly, when the bottle is in stage 3, there can be one bottle each in stage 1 and stage 2. So, after each minute, we get a new bottle at the end of stage 3. Hence, the average time taken to manufacture 1 bottle is:

```

Without pipelining = 9/3 minutes = 3m

IFS | | | | | |

| | | IFS | | |

| | | | | IFS (9 minutes)

With pipelining = 5/3 minutes = 1.67m

IFS | |

| IFS | |

| IFS (5 minutes)

```

Thus, pipelined operation increases the efficiency of a system.

### Design of a basic pipeline

In a pipelined processor, a pipeline has two ends, the input end and the output end. Between these ends, there are multiple stages/segments such that output of one stage is connected to input of next stage and each stage performs a specific operation.

Interface registers are used to hold the intermediate output between two stages. These interface registers are also called latch or buffer.

All the stages in the pipeline along with the interface registers are controlled by a common clock.

## **Execution in a pipelined processor:**

Execution sequence of instructions in a pipelined processor can be visualized using a space-time diagram. For example, consider a processor having 4 stages and let there be 2 instructions to be executed. We can visualize the execution sequence through the following space-time diagrams:

## Non overlapped execution:

| STAGE /<br>CYCLE | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     |

|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| <b>S</b> 1       | $I_1$ |       |       |       | $I_2$ |       |       |       |

| S2               |       | $I_1$ |       |       |       | $I_2$ |       |       |

| S3               |       |       | $I_1$ |       |       |       | $I_2$ |       |

| S4               |       |       |       | $I_1$ |       |       |       | $I_2$ |

Total time = 8 Cycle

**Overlapped execution:**

| STAGE/CYCLE | 1     | 2     | 3     | 4     | 5     |

|-------------|-------|-------|-------|-------|-------|

| S1          | $I_1$ | $I_2$ |       |       |       |

| S2          |       | $I_1$ | $I_2$ |       |       |

| S3          |       |       | $I_1$ | $I_2$ |       |

| S4          |       |       |       | $I_1$ | $I_2$ |

Total time = 5 Cycle

# **Pipeline Stages**

RISC processor has 5 stage instruction pipeline to execute all the instructions in the RISC instruction set. Following are the 5 stages of RISC pipeline with their respective operations:

## **Stage 1 (Instruction Fetch)**

In this stage the CPU reads instructions from the address in the memory whose value is present in the program counter.

## **Stage 2 (Instruction Decode)**

In this stage, instruction is decoded and the register file is accessed to get the values from the registers used in the instruction.

## **Stage 3 (Instruction Execute)**

In this stage, ALU operations are performed.

## **Stage 4 (Memory Access)**

In this stage, memory operands are read and written from/to the memory that is present in the instruction.

## **Stage 5 (Write Back)**

In this stage, computed/fetched value is written back to the register present in the instructions.

# Performance of a pipelined processor

Consider a 'k' segment pipeline with clock cycle time as 'Tp'. Let there be 'n' tasks to be completed in the pipelined processor. Now, the first instruction is going to take 'k' cycles to come out of the pipeline but the other 'n-1' instructions will take only '1' cycle each, i.e, a total of 'n-1' cycles. So, time taken to execute 'n' instructions in a pipelined processor:

$$ET_{pipeline} = k + n - 1 \text{ cycles}$$

$$= (k + n - 1) \text{ Tp}$$

In the same case, for a non-pipelined processor, execution time of 'n' instructions will be:

$$ET_{\text{non-pipeline}} = n * k * Tp$$

So, speedup (S) of the pipelined processor over non-pipelined processor, when 'n' tasks are executed on the same processor is:

S = Performance of pipelined processor /

Performance of Non-pipelined processor

As the performance of a processor is inversely proportional to the execution time, we have,

$$\begin{split} S &= ET_{\text{non-pipeline}} / ET_{\text{pipeline}} \\ &=> S = \left[ n * k * Tp \right] / \left[ (k + n - 1) * Tp \right] \\ S &= \left[ n * k \right] / \left[ k + n - 1 \right] \end{split}$$

When the number of tasks 'n' are significantly larger than k, that is,  $n \gg k$

$$S = n * k / n$$

$$S = k$$

where 'k' are the number of stages in the pipeline.

Also, **Efficiency** = Given speed up / Max speed up =  $S / S_{max}$  We know that, Smax = k So, **Efficiency** = S / k

**Throughput** = Number of instructions / Total time to complete the instructions

So, **Throughput** = n / (k + n - 1) \* Tp

Note: The cycles per instruction (CPI) value of an ideal pipelined processor is 1

## Problem (example):

Consider a pipeline having 4 phases with duration 60, 50, 90 and 80 ns. Given latch delay is 10 ns. Calculate-

- 1. Pipeline cycle time

- 2. Non-pipeline execution time

- 3. Speed up ratio

- 4. Pipeline time for 1000 tasks

- 5. Sequential time for 1000 tasks

- 6. Throughput

## **Solution-**

Given-

- Four stage pipeline is used k=4

- Delay of stages = 60, 50, 90 and 80 ns

- Latch delay or delay due to each register = 10 ns

## 1: Pipeline Cycle Time-

Cycle time

- = Maximum delay due to any stage + Delay due to its register

- = Max { 60, 50, 90, 80 } + 10 ns = 90 ns + 10 ns = 100 ns

### 2: Non-Pipeline Execution Time- (no latches hence latch delay=0)

Non-pipeline execution time for one instruction

= 60 ns + 50 ns + 90 ns + 80 ns = 280 ns

### 3: Speed Up Ratio-

Speed up

- = Non-pipeline execution time / Pipeline execution time

- = 280 ns / 100 ns

- = 2.8

#### 4: Pipeline Time For 1000 Tasks-

Pipeline time for 1000 tasks

- = Time taken for 1st task + Time taken for remaining 999 tasks

- = 1 x 4 clock cycles + 999 x 1 clock cycle

- = 4 x cycle time + 999 x cycle time

- $= 4 \times 100 \text{ ns} + 999 \times 100 \text{ ns}$

- = 400 ns + 99900 ns

- = 100300 ns

## 5: Sequential Time For 1000 Tasks-

Non-pipeline time for 1000 tasks

- = 1000 x Time taken for one task

- $= 1000 \times 280 \text{ ns}$

- = 280000 ns

### 6: Throughput-

Throughput for pipelined execution

- = Number of instructions executed per unit time

- = 1000 tasks / 100300 ns

# <u>Dependencies in a pipelined processor</u> <u>Pipeline hazards</u>

There are mainly three types of dependencies possible in a pipelined processor. These are :

- 1) Structural Dependency

- 2) Control Dependency

- 3) Data Dependency

These dependencies may introduce stalls in the pipeline.

**Stall**: A stall is a cycle in the pipeline without new input.

## 1. Structural dependency

This dependency arises due to the resource conflict in the pipeline. A resource conflict is a situation when more than one instruction tries to access the same resource in the same cycle. A resource can be a register, memory, or ALU.

#### Example:

| INSTRUCTION / CYCLE | 1       | 2       | 3       | 4       | 5  |

|---------------------|---------|---------|---------|---------|----|

| $\mathbf{I}_1$      | IF(Mem) | ID      | EX      | Mem     |    |

| $I_2$               |         | IF(Mem) | ID      | EX      |    |

| $I_3$               |         |         | IF(Mem) | ID      | EX |

| $\mathbf{I}_4$      |         |         |         | IF(Mem) | ID |

- In the above scenario, in cycle 4, instructions I<sub>1</sub> and I<sub>4</sub> are trying to access same resource (Memory) which introduces a resource conflict.

- To avoid this problem, we have to keep the instruction on wait until the required resource (memory in our case) becomes available. This wait will introduce stalls in the pipeline as shown below:

| CYCLE | 1       | 2       | 3       | 4   | 5   | 6   | 7       | 8 |

|-------|---------|---------|---------|-----|-----|-----|---------|---|

| $I_1$ | IF(Mem) | ID      | EX      | Mem | WB  |     |         |   |

| $I_2$ |         | IF(Mem) | ID      | EX  | Mem | WB  |         |   |

| $I_3$ |         |         | IF(Mem) | ID  | EX  | Mem | WB      |   |

| $I_4$ |         |         |         | _   | _   | _   | IF(Mem) |   |

### **Solution for structural dependency**

To minimize structural dependency stalls in the pipeline, we use a hardware mechanism called Renaming. **Renaming:** According to renaming, we divide the memory into two independent modules used to store the instruction and data separately called Code memory (CM) and Data memory (DM) respectively. CM will contain all the instructions and DM will contain all the operands that are required for the instructions.

| INSTRUCTION/<br>CYCLE | 1      | 2      | 3      | 4      | 5      | 6      | 7      |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|

| $I_1$                 | IF(CM) | ID     | EX     | DM     | WB     |        |        |

| $I_2$                 |        | IF(CM) | ID     | EX     | DM     | WB     |        |

| $I_3$                 |        |        | IF(CM) | ID     | EX     | DM     | WB     |

| $I_4$                 |        |        |        | IF(CM) | ID     | EX     | DM     |

| $I_5$                 |        |        |        |        | IF(CM) | ID     | EX     |

| $I_6$                 |        |        |        |        |        | IF(CM) | ID     |

| $I_7$                 |        |        |        |        |        |        | IF(CM) |

### 2. Control Dependency (Branch Hazards)

This type of dependency occurs during the transfer of control instructions such as BRANCH, CALL, JMP, etc. On many instruction architectures, the processor will not know the target address of these instructions when it needs to insert the new instruction into the pipeline. Due to this, unwanted instructions are fed to the pipeline.

Consider the following sequence of instructions in the program:

100: I<sub>1</sub>

101: I<sub>2</sub> (JMP 250)

102: I<sub>3</sub>

250: BI<sub>1</sub>

Expected output:  $I_1 \rightarrow I_2 \rightarrow BI_1$

NOTE: Generally, the target address of the JMP instruction is known after ID stage only.

| INSTRUCTION/ CYCLE | 1  | 2  | 3           | 4   | 5   | 6   |

|--------------------|----|----|-------------|-----|-----|-----|

| $I_1$              | IF | ID | EX          | MEM | WB  |     |

| $I_2$              |    | IF | ID (PC:250) | EX  | Mem | WB  |

| $I_3$              |    |    | IF          | ID  | EX  | Mem |

| $BI_1$             |    |    |             | IF  | ID  | EX  |

Output Sequence:  $I_1 \rightarrow I_2 \rightarrow I_3 \rightarrow BI_1$

So, the output sequence is not equal to the expected output, that means the pipeline is not implemented correctly.

To eliminate this problem we need to stop the Instruction fetch until we get target address of branch instruction. This can be implemented by introducing delay slot until we get the target address.

| INSTRUCTION/ CYCLE | 1  | 2  | 3           | 4   | 5   | 6  |

|--------------------|----|----|-------------|-----|-----|----|

| $I_1$              | IF | ID | EX          | MEM | WB  |    |

| $I_2$              |    | IF | ID (PC:250) | EX  | Mem | WB |

| Delay              | _  | _  | _           | _   | _   | _  |

| $BI_1$             |    |    |             | IF  | ID  | EX |

Output Sequence:  $I_1 \rightarrow I_2 \rightarrow Delay$  (Stall)  $\rightarrow BI_1$

As the delay slot performs no operation, this output sequence is equal to the expected output sequence. But this slot introduces stall in the pipeline.

## **Solution for Control dependency:**

Branch Prediction is the method through which stalls due to control dependency can be eliminated. In this at 1st stage prediction is done about which branch will be taken. For branch prediction Branch penalty is zero.

**Branch penalty:** The number of stalls introduced during the branch operations in the pipelined processor is known as branch penalty.

**NOTE:** As we see that the target address is available after the ID stage, so the number of stalls introduced in the pipeline is 1. Suppose, the branch target address would have been present after the ALU stage, there would have been 2 stalls. Generally, if the target address is present after the  $k^{th}$  stage, then there will be (k-1) stalls in the pipeline.

Total number of stalls introduced in the pipeline due to branch instructions = **Branch frequency \* Branch Penalty**

## 3. Data Dependency (Data Hazard)

Let us consider an ADD instruction S, such that

S: ADD R1, R2, R3

Addresses read by  $S = I(S) = \{R2, R3\}$

Addresses written by  $S = O(S) = \{R1\}$

Now, we say that instruction S2 depends in instruction S1, when

$[I(S1) \cap O(S2)] \cup [O(S1) \cap I(S2)] \cup [O(S1) \cap O(S2)] \neq \phi$

This condition is called Bernstein condition.

#### Three cases exist:

- Flow (data) dependence:  $O(S1) \cap I(S2)$ ,  $S1 \rightarrow S2$  and S1 writes after something read by S2

- Anti-dependence:  $I(S1) \cap O(S2)$ ,  $S1 \rightarrow S2$  and S1 reads something before S2 overwrites it

- Output dependence:  $O(S1) \cap O(S2)$ ,  $S1 \rightarrow S2$  and both write the same memory location.

**Example:** Let there be two instructions I1 and I2 such that:

I1: ADD R1, R2, R3 I2: SUB R4, R1, R2

When the above instructions are executed in a pipelined processor, then data dependency condition will occur, which means that  $I_2$  tries to read the data before  $I_1$  writes it, therefore,  $I_2$  incorrectly gets the old value from  $I_1$ .

| INSTRUCTION / CYCLE | 1  | 2  | 3             | 4  |

|---------------------|----|----|---------------|----|

| $I_1$               | IF | ID | EX            | DM |

| $I_2$               |    | IF | ID(Old value) | EX |

To minimize data dependency stalls in the pipeline, **operand forwarding** is used.

**Operand Forwarding:** In operand forwarding, we use the interface registers present between the stages to hold intermediate output so that dependent instruction can access new value from the interface register directly.

Considering the same example:

I1: ADD R1, R2, R3

I2: SUB R4, R1, R2

| 12. 8 0 2 10., 101, 102 |    |    |    |    |

|-------------------------|----|----|----|----|

| INSTRUCTION / CYCLE     | 1  | 2  | 3  | 4  |

| $I_1$                   | IF | ID | EX | DM |

| $I_2$                   |    | IF | ID | EX |

#### **Data Hazards**

Data hazards occur when instructions that exhibit data dependence, modify data in different stages of a pipeline. Hazard cause delays in the pipeline. There are mainly three types of data hazards:

- 1) RAW (Read after Write) [Flow/True data dependency]

- 2) WAR (Write after Read) [Anti-Data dependency]

- 3) WAW (Write after Write) [Output data dependency]

Let there be two instructions I and J, such that J follow I. Then,

1) RAW hazard occurs when instruction J tries to read data before instruction, I writes it. Eg:

I: R2 < -R1 + R3

J: R4 < -R2 + R3

- 2) WAR hazard occurs when instruction J tries to write data before instruction I reads it. Eg:

- I: R2 < -R1 + R3

- J: R3 < -R4 + R5

- 3) WAW hazard occurs when instruction J tries to write output before instruction I writes it. Eg:

- I: R2 < -R1 + R3

- J: R2 < -R4 + R5

WAR and WAW hazards occur during the out-of-order execution of the instructions.

## **Pipelining: Types and Stalling**

## **Types of pipeline**

## 1. Uniform delay pipeline:

- In this type of pipeline, all the stages will take same time to complete an operation.

- In uniform delay pipeline, Cycle Time (Tp) = Stage Delay

- If buffers are included between the stages then,

Cycle Time (Tp) = Stage Delay + Buffer Delay

#### 2. Non-Uniform delay pipeline:

- In this type of pipeline, different stages take different time to complete an operation.

- In this type of pipeline, Cycle Time (Tp) = Maximum (Stage Delay)

- For example, if there are 4 stages with delays, 1 ns, 2 ns, 3 ns, and 4 ns, then

Tp = Maximum (1 ns, 2 ns, 3 ns, 4 ns) = 4 ns

• If buffers are included between the stages,

Tp = Maximum (Stage delay + Buffer delay)

**Example:** Consider a 4-segment pipeline with stage delays (2 ns, 8 ns, 3 ns, 10 ns). Find the time taken to execute 100 tasks in the above pipeline.

**Solution:** As the above pipeline is a non-linear pipeline,

Tp = max (2, 8, 3, 10) = 10 ns

We know that  $ET_{pipeline} = (k + n - 1) Tp = (4 + 100 - 1) 10 ns = 1030 ns$

NOTE: MIPS = Million instructions per second

#### Performance of pipeline with stalls

Speed Up (S) = Performance<sub>pipeline</sub> / Performance<sub>non-pipeline</sub>

=> S = Average Execution Time<sub>non-pipeline</sub> / Average Execution Time<sub>pipeline</sub>

$=>S=CPI_{\text{non-pipeline}}*Cycle\ Time_{\text{non-pipeline}} \ /\ CPI_{\text{pipeline}}*Cycle\ Time_{\text{pipeline}}$

Ideal CPI of the pipelined processor is '1'. But due to stalls, it becomes greater than '1'.

=>  $S=CPI_{\text{non-pipeline}}*$  Cycle Time\_{non-pipeline} / (1 + Number of stalls per Instruction) \* Cycle Time\_{pipeline}

As Cycle Time<sub>non-pipeline</sub> = Cycle Time<sub>pipeline</sub>,

#### Speed Up (S) = $CPI_{\text{non-pipeline}} / (1 + \text{Number of stalls per instruction})$

**<u>Dynamic Instruction Scheduling:</u>** If the programmer is aware of a pipelined architecture then it may be possible to rewrite programs statically either manually or using an optimising compiler to separate data dependencies otherwise they must be detected and resolved by hardware at runtime.

Scoreboarding: A scoreboard is a centralized control logic which uses forwarding logic and register tagging to keep track of the status of registers and multiple functional units. An issued instruction whose registers are not available is forwarded to a reservation station (buffer) associated with the functional unit it will use. When functional units generate new results, some data dependencies can be resolved. When all registers have valid data the scoreboard enables the instruction execution. Similarly, when a functional unit finishes, it signals the scoreboard to release the register resources.

# **Arithmetic Pipeline and Instruction Pipeline**

## 1. Arithmetic Pipeline:

An arithmetic pipeline divides an arithmetic problem into various sub problems for execution in various pipeline segments. It is used for floating point operations, multiplication and various other computations.

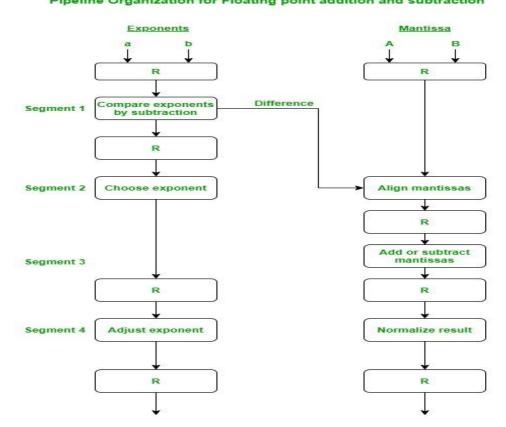

## Floating point addition using arithmetic pipeline:

The following sub operations are performed in this case:

- Compare the exponents.

- Align the mantissas.

- Add or subtract the mantissas.

- Normalise the result

First, the two exponents are compared and the larger of two exponents is chosen as the result exponent. The difference in the exponents then decides how many times we must shift the smaller exponent to the right. Then after shifting of exponent, both the mantissas get aligned. Finally, the addition of both numbers take place followed by normalisation of the result in the last segment.

## **Example:**

Let us consider two numbers,

X=0.3214\*10^3 and Y=0.4500\*10^2

## **Explanation:**

First of all the two exponents are subtracted to give 3-2=1. Thus 3 becomes the exponent of result and the smaller exponent is shifted 1 time to the right to give

Y=0.0450\*10^3

Finally, the two numbers are added to produce

Z=0.3664\*10^3

As the result is already normalized the result remains the same.

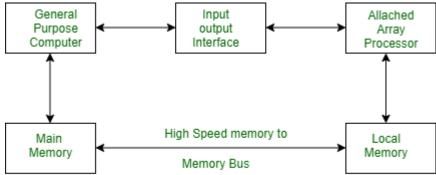

The process or flowchart arithmetic pipeline for floating point addition is shown in the diagram.

Pipeline Organization for Floating point addition and subtraction

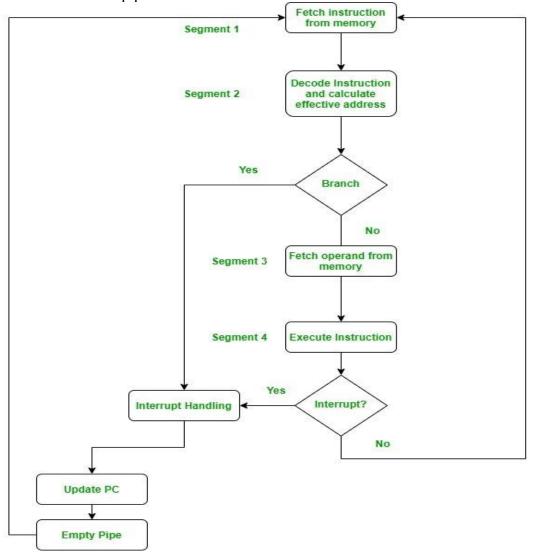

### 2. Instruction Pipeline:

- In this a stream of instructions can be executed by overlapping fetch, decode and execute phases of an instruction cycle. This type of technique is used to increase the throughput of the computer system. An instruction pipeline reads instruction from the memory while previous instructions are being executed in other segments of the pipeline. Thus we can execute multiple instructions simultaneously. The pipeline will be more efficient if the instruction cycle is divided into segments of equal duration.

- In the most general case computer needs to process each instruction in following sequence of steps:

- o Fetch the instruction from memory (FI)

- o Decode the instruction (DA)

- Calculate the effective address

- o Fetch the operands from memory (FO)

- o Execute the instruction (EX)

- o Store the result in the proper place

The flowchart for instruction pipeline is shown below.

Let us see an example of instruction pipeline.

**Example:**

|             | Stage | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 |

|-------------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|

|             | 1     | FI | DA | FO | EX |    |    |    |    |    |    |    |    |    |

| Instruction | 2     |    | FI | DA | FO | EX |    |    |    |    |    |    |    |    |

| Branch      | 3     |    |    | FI | DA | FO | EX |    |    |    |    |    |    |    |

|             | 4     |    |    |    | FI |    |    | FI | DA | FO | EX |    |    |    |

|             | 5     |    |    |    |    |    |    |    | FI | DA | FO | EX |    |    |

|             | 6     |    |    |    |    |    |    |    |    | FI | DA | FO | EX |    |

|             | 7     |    |    |    |    |    |    |    |    |    | FI | DA | FO | EX |

Here the instruction is fetched on first clock cycle in segment 1.

- Now it is decoded in next clock cycle, then operands are fetched and finally the instruction is executed. We can see that here the fetch and decode phase overlap due to pipelining. By the time the first instruction is being decoded, next instruction is fetched by the pipeline.

- In case of third instruction we see that it is a branched instruction. Here when it is being decoded 4th instruction is fetched simultaneously. But as it is a branched instruction it may point to some other instruction when it is decoded. Thus, fourth instruction is kept on hold until the branched instruction is executed. When it gets executed then the fourth instruction is copied back and the other phases continue as usual.

# **Superscalar Architecture**

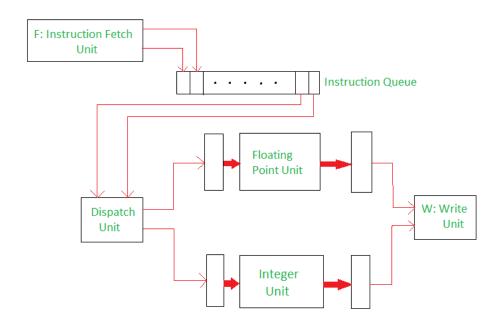

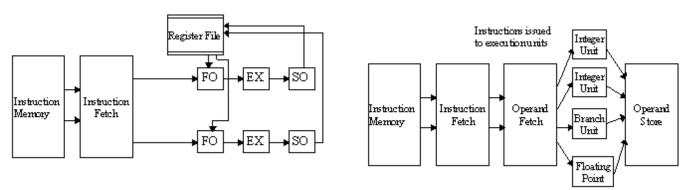

A more useful approach is to equip the processor with multiple processing units to handle several instructions in parallel in each processing stage. With this arrangement, several instructions start execution in the same clock cycle and the process is said to use multiple issue. Such processors are capable of achieving an instruction execution throughput of more than one instruction per cycle. They are known as 'Superscalar Processors'.

**Processor with Two Execution Units**

In the above diagram, there is a processor with two execution units; one for integer and one for floating point operations. The instruction fetch unit is capable of reading the instructions at a time and storing them in the instruction queue. In each cycle, the dispatch unit retrieves and decodes up to two instructions from the front of the queue. If there is one integer, one floating point instruction and no hazards, both the instructions are dispatched in the same clock cycle.

A scalar processor executes scalar instructions, that is instructions operating on single quantity operands such as integers. As we have seen, the design of such a processor may be pipelined where the staggered use of the pipeline can improve instruction throughput. A superscalar processor is one which executes more than one scalar instruction concurrently. This is achieved by having a number of independent pipelines. A limited form of superscalar operation is present in processors that have, for example, separate integer and floating point units. After the decode stage the instructions are sent to the appropriate unit and can execute in parallel. True superscalar operation can only be achieved by fetching a number of instructions simultaneously and executing them simultaneously.

Superscalar Dual Pipeline Processor

Superscalar design with multiple specialised execution units

The objective of superscalar design is to improve performance by exploiting instruction level parallelism in user programs. We might expect that doubling the number of pipelines would double performance, but we have seen the problems caused by pipeline hazards in a single pipeline and can see that this problem is much more critical for superscalar processors and that some of the pipelines will be stalling. One of the characteristics of RISC designs is that the processor has a simplified instruction set architecture resulting in fewer data interdependencies. For this reason, virtually all superscalar designs have been based on a RISC architecture. The superscalar degree is low due to limited instruction parallelism that can be exploited in ordinary programs.

Instruction issue and completion policies are critical to superscalar processor performance. When instructions are issued (i.e. initiation of their execution in functional units) in program order it is called *in-order issue*. When program order is violated, *out-of-order issue* is being practiced. When instructions must be completed (i.e. have altered register and/or memory) in program order, it is called *in-order completion*, otherwise *out-of-order* completion may result. In-order issue is easier to implement but may not yield the optimal performance. Proper scheduling can avoid stalling the pipelines. A number of possible scheduling policies are possible. In the examples below, the pipeline cycle is the minimum time between consecutive exchanges between each stage of the pipeline.

#### 1) In-Order Issue with In-Order Completion:

Assume we have a superscalar pipeline capable of fetching and decoding two instructions at a time. Let's say there are three separate functional units and that there are two instances of the writeback pipeline stage.

Let's say we have six instructions with the following constraints:

- I1 requires two cycles to execute.

- I3 and I4 conflict for the same functional unit.

- I5 depends on the value produced by I4.

- I5 and I6 conflict for a functional unit.

Instructions are only decoded up to the point of a dependency or resource conflict. No additional instructions are decoded until the conflict is resolved. This means a maximum of two instructions can be in the execute stage as later instructions have a time dependency on earlier ones executing first.

| Cycle | I  | ecode) |   | Execute |    | Writeback |   |    |    |

|-------|----|--------|---|---------|----|-----------|---|----|----|

| 1     | I1 | I2     |   |         |    |           |   |    |    |

| 2     | I3 | I4     |   | I1      | 12 |           |   |    |    |

| 3     | I3 | I4     |   | I1      |    |           |   |    |    |

| 4     |    | I4     |   |         |    | I3        |   | I1 | I2 |

| 5     | 15 | I6     |   |         |    | I4        |   |    |    |

| 6     |    | I6     |   |         | I5 |           |   | 13 | I4 |

| 7     |    |        |   |         | I6 |           |   |    |    |

| 8     |    |        |   |         |    |           |   | 15 | I6 |

|       |    |        | l |         |    |           | l |    |    |

## 2) In-Order Issue with Out-of-Order Completion:

Using the same set of instructions, the next diagram illustrates the effect of allowing some instructions to complete out-of-order. With out-of-order completion, any number of instructions may be in the execution stage, limited only by the machine's parallelism. Instruction issuing in any one pipeline is stalled by a resource conflict, data dependency or procedural dependency.

| Cycle | Ι  | Decode |    | Execute |    |    | Write | back |

|-------|----|--------|----|---------|----|----|-------|------|

| 1     | I1 | I2     |    |         |    | ΙΓ |       |      |

| 2     | 13 | I4     | I1 | 12      |    |    |       |      |

| 3     |    | I4     | I1 |         | I3 | I: | 2     |      |

| 4     | 15 | I6     |    |         | I4 | I  | 1     | I3   |

| 5     |    | I6     |    | 15      |    | I  | 4     |      |

| 6     |    |        |    | I6      |    | I. | 5     |      |

| 7     |    |        |    |         |    | I  | 6     |      |

- Note that I2 is allowed to complete before I1. I5 depends on the value produced by I4 and cannot be issued until cycle 5.

- Out-of-order completion requires more complex instruction-issue logic than in-order completion.

It is more difficult to deal with instruction interrupts and exceptions. When an interrupt occurs, the processor must take into account that instructions ahead of the instruction that caused the interrupt may have already completed.

- The time from decoding the first instruction to writing the last is 7 cycles.

## 3) Out-of-Order Issue with Out-of-Order Completion:

To allow out-of-order issue, it is necessary to decouple the decode and execute stages of the pipeline. When an instruction has been decoded it is placed in a buffer known as an instruction window. As long as this buffer is not full, the processor can continue to fetch and decode new instructions. When a functional unit becomes available an instruction from the window may be issued. Any instruction that needs the functional unit and which has no conflicts or dependencies to block it may be selected.

| Cycle | I  | Decode | Window   | Execute |    |    | Writ | eback |

|-------|----|--------|----------|---------|----|----|------|-------|

| 1     | I1 | I2     |          |         |    |    |      |       |

| 2     | 13 | I4     | I1,I2    | I1      | 12 |    |      |       |

| 3     | 15 | I6     | I3,I4    | I1      |    | I3 | 12   |       |

| 4     |    |        | I4,I5,I6 |         | I6 | I4 | I1   | I3    |

| 5     |    |        | 15       |         | 15 |    | I4   | I6    |

| 6     |    |        |          |         |    |    | I5   |       |

• Note that it is possible to issue I6 before I5 as I5 has a dependency on I4. The time from decoding the first instruction to writing the last is 6 cycles.

The instruction window can be centralised or distributed. A centralised instruction window holds all instructions irrespective of their type. In the distributed approach, instruction buffers called *reservation stations* are placed in front of each functional unit. Decoded instructions are routed to the appropriate reservation station and subsequently issued to the functional unit when it is free and all operands for the instruction have been received by the reservation station.

Advantages of Superscalar Architecture:

- o In a Superscalar Processor, the detrimental effect on performance of various hazards becomes even more pronounced.

- o The compiler can avoid many hazards through judicious selection and ordering of instructions.

- o The compiler should strive to interleave floating point and integer instructions. This would enable the dispatch unit to keep both the integer and floating point units busy most of the time.

- o In general, high performance is achieved if the compiler is able to arrange program instructions to take maximum advantage of the available hardware units.

Disadvantages of Superscalar Architecture:

o Due to this type of architecture, problem in scheduling can occur.

### COMPARISON BETWEEN PIPELINING & SUPERSCALAR

| Pipelining                                             | Superscalar                                          |

|--------------------------------------------------------|------------------------------------------------------|

| divides an instruction into steps, and since each      | involves the processor being able to issue multiple  |

| step is executed in a different part of the processor, | instructions in a single clock with redundant        |

| multiple instructions can be in different "phases"     | facilities to execute an instruction within a single |

| each clock.                                            | core                                                 |

| once one instruction was done decoding and went        | multiple execution subunits able to do the same      |

| on towards the next execution subunit                  | thing in parallel                                    |

| Sequencing unrelated activities such that they use     | Multiple sub-components capable of doing the         |

| different components at the same time                  | same task simultaneously, but with the processor     |

|                                                        | deciding how to do it.                               |

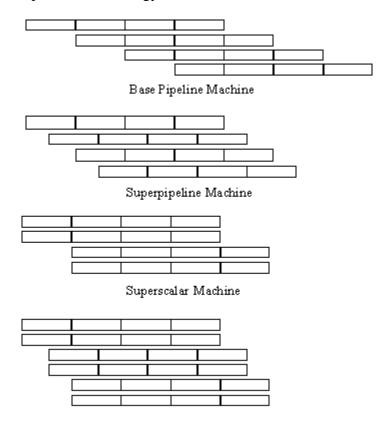

# **Superpipelining**

An alternative approach to achieving better performance is superpipelining. Superpipelining exploits the fact that many pipeline stages perform tasks that require less than half a clock cycle. A doubled internal clock speed allows those stages to perform two tasks during one external clock cycle. In a superpipelined processor of degree n, the pipeline cycle time is 1/n of the base cycle. Stages that require the full base cycle to complete can be strung into a series of shorter stages, effectively increasing the length of the pipeline and matching the execution latency of each stage. An number of instructions may be in various parts of the execution stage. As a comparison, where an execution operation takes 1

cycle in the base scalar processor, the same operation is implemented as n short cycles in a superpipelined processor with the same operation technology.

Superscalar Superpipelined Machine

Both the superpipeline and the superscalar implementations have the same number of instructions executing at the same time in the steady state. The superpipelined processor falls behind the superscalar processor at the start of the program and after each branch instruction.

The following terms are used for comparison.

- The *scalar base machine* is a single multi-stage pipeline processor.

- The *pipeline cycle* for the scalar base machine is assumed to be 1 time unit called the base cycle.

- The *instruction issue rate* is the number of instructions issued per cycle.

- The *instruction issue latency* is the time required between the issuing of two adjacent instructions.

- *Simple operation latency* is the time taken to execute simple operations, such as add, load, store, branch, move etc. which make up the vast majority of instructions executed by the processor.

- Complex instructions are those requiring an order of magnitude longer latency such as divides, cache misses.

- The *instruction level parallelism* is the maximum number of instructions that can be simultaneously executed in the pipeline.

| Machine Type                                                      | Scalar base<br>machine of k<br>pipeline stages | Superscalar<br>machine of<br>degreem | Superpipeline<br>machine of<br>degreen | Superpipeline<br>superscalar machine<br>of degree (m, n) |

|-------------------------------------------------------------------|------------------------------------------------|--------------------------------------|----------------------------------------|----------------------------------------------------------|

| Machine Pipeline<br>Cycle                                         | l (base cycle)                                 | 1                                    | 1/n                                    | 1/n                                                      |

| Instruction Issue<br>Rate                                         | 1                                              | m                                    | 1                                      | m                                                        |

| Instruction Issue<br>Latency                                      | 1                                              | 1                                    | l/n                                    | 1/n                                                      |

| Simple Operation<br>Latency                                       | 1                                              | 1                                    | l = (n x 1/n)                          | 1 = (n x 1/n)                                            |

| Instruction Level<br>Parallelism to fully<br>utilise the pipeline | 1                                              | m                                    | n                                      | nn                                                       |

Design Parameters for Pipeline Processors

- In the scalar base machine one instruction is issued per cycle, with one cycle latency for simple operations and one cycle latency between instructions. The instruction pipeline can be fully utilised if successive instructions can enter it continuously at the rate of one per cycle.

- In a superpipelined superscalar design of degree (m,n) the machine executes m instructions every cycle with a pipeline cycle 1/n of the base cycle. Simple operation latency is n pipeline cycles. The level of parallelism required to fully utilise this machine is mn instructions.

- The superscalar approach depends on the ability to execute multiple instructions in parallel. A combination of the compiler-based optimisation and various hardware techniques can be used to maximise instruction level parallelism.

#### COMPARISON BETWEEN SUPERPIPELINING & SUPERSCALAR

- Super-pipelining attempts to increase performance by reducing the clock cycle time. It achieves that by making each pipeline stage very shallow, resulting in a large number of pipe stages. A shorter clock cycle means a faster clock. As long as your cycles per instruction (CPI) doesn't change, a faster clock means better performance. Super-pipelining works best with code that doesn't branch often, or has easily predicted branches.

- Superscalar attempts to increase performance by executing multiple instructions in parallel. If we can issue more instructions every cycle, without decreasing clock rate, then CPI decreases, therefore increasing performance.

- Superscalar breaks into two broad categories: In-order and out-of-order.

- o In-order superscalar mainly provides benefit to code with instruction-level parallelism among a small window of consecutive instructions.

- Out-of-order superscalar allows the pipeline to find parallelism across larger windows of code, and to hide latencies associated with long-running instructions. (Example: load instructions that miss the cache.)

#### NOTE:

- o Super-pipelining seeks to improve the sequential instruction rate, while superscalar seeks to improve the parallel instruction rate.

- o Most modern processors are both superscalar and super-pipelined. They have deep pipelines to achieve high clock rates, and wide instruction issue to make use of instruction level parallelism.

# **Instruction-level parallelism**

- Instruction-level parallelism (ILP) is a measure of how many of the instructions in a computer program can be executed simultaneously.

- ILP must not be confused with concurrency, since **ILP** is about parallel execution of a sequence of instructions belonging to a specific thread of execution of a process (that is a running program with its set of resources for example its address space, a set of registers, its identifiers, its state, program counter, and more). Conversely, **concurrency** regards with the threads of one or different processes being assigned to a CPU's core in a strict alternance or in true parallelism if there are enough CPU's cores, ideally one core for each runnable thread.

There are two approaches to instruction level parallelism: Hardware and Software.

Hardware level works upon dynamic parallelism, whereas the software level works on static

parallelism. Dynamic parallelism means the processor decides at run time which instructions to

execute in parallel, whereas static parallelism means the compiler decides which instructions to

execute in parallel. The Pentium processor works on the dynamic sequence of parallel execution,

but the Itanium processor works on the static level parallelism.

Consider the following program:

```

1 e = a + b

2 f = c + d

3 m = e * f

```

- Operation 3 depends on the results of operations 1 and 2, so it cannot be calculated until both of them are completed. However, operations 1 and 2 do not depend on any other operation, so they can be calculated simultaneously. If we assume that each operation can be completed in one unit of time then these three instructions can be completed in a total of two units of time, giving an ILP of 3/2(as 1 and 2 can execute concurrently and require 1 unit time and instruction 3 require 1 unit time).

- A goal of compiler and processor designers is to identify and take advantage of as much ILP as

possible. Ordinary programs are typically written under a sequential execution model where

instructions execute one after the other and in the order specified by the programmer. ILP allows

the compiler and the processor to overlap the execution of multiple instructions or even to change

the order in which instructions are executed.

Micro-architectural techniques that are used to exploit ILP include:

- Instruction pipelining where the execution of multiple instructions can be partially overlapped.

- Superscalar execution, VLIW, and the closely related explicitly parallel instruction computing concepts, in which multiple execution units are used to execute multiple instructions in parallel.

- Out-of-order execution where instructions execute in any order that does not violate data dependencies. Note that this technique is independent of both pipelining and superscalar execution. Current implementations of out-of-order execution dynamically (i.e., while the program is executing and without any help from the compiler) extract ILP from ordinary programs. An alternative is to extract this parallelism at compile time and somehow convey this information to the hardware. Due to the complexity of scaling the out-of-order execution technique, the industry has re-examined instruction sets which explicitly encode multiple independent operations per instruction.

- Register renaming which refers to a technique used to avoid unnecessary serialization of program

operations imposed by the reuse of registers by those operations, used to enable out-of-order

execution.

- Speculative execution which allows the execution of complete instructions or parts of instructions before being certain whether this execution should take place. A commonly used form of speculative execution is control flow speculation where instructions past a control flow instruction

(e.g., a branch) are executed before the target of the control flow instruction is determined. Several other forms of speculative execution have been proposed and are in use including speculative execution driven by value prediction, memory dependence prediction and cache latency prediction.

• Branch prediction which is used to avoid stalling for control dependencies to be resolved. Branch prediction is used with speculative execution.

**Note:** It is known that the ILP is exploited by both the compiler and hardware support but the compiler also provides inherent and implicit ILP in programs to hardware by compilation optimization. Some optimization techniques for extracting available ILP in programs would include scheduling, register allocation/renaming, and memory access optimization.

- To obtain substantial performance enhancements, we must exploit ILP across multiple basic blocks.

- The simplest and most common way to increase the amount of parallelism available among instructions is to exploit parallelism among iterations of a loop. This type of parallelism is often called loop-level parallelism.

## Example 1

```

for (i=1; i<=1000; i= i+1)

x[i] = x[i] + y[i];

```

• This is a parallel loop. Every iteration of the loop can overlap with any other iteration, although within each loop iteration there is little opportunity for overlap.

## Example 2

```

for (i=1; i<=100; i= i+1){  a[i] = a[i] + b[i];  //s1   b[i+1] = c[i] + d[i];  //s2 }

```

Statement s1 uses the value assigned in the previous iteration by statement s2, so there is a loop-carried dependency between s1 and s2.

# **VLIW Architecture:**

- Very Long Instruction Word (VLIW) architecture in P-DSPs (programmable DSP) increases the

number of instructions that are processed per cycle. It is a concatenation of several short

instructions and requires multiple execution units running in parallel, to carry out the instructions

in a single cycle. A language compiler or pre-processor separates program instructions into basic

operations and places them into VLIW processor which then disassembles and transfers each

operation to an appropriate execution unit.

- VLIW P-DSPs have a number of processing units (data paths) i.e. they have a number of ALUs, MAC units, shifters, etc. The VLIW is accessed from memory and is used to specify the operands and operations to be performed by each of the data paths.

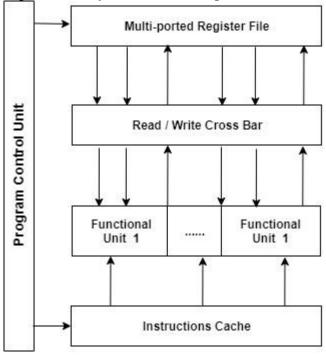

**VLIW Architecture**

- As shown in figure, the multiple functional units share a common multi-ported register file for

fetching the operands and storing the results. Parallel random access by the functional units to the

register file is facilitated by the read/write cross bar. Execution of the operations in the functional

units is carried out concurrently with the load/ store operation of data between a RAM and the

register file.

- The performance gains that can be achieved with VLIW architecture depends on the degree of parallelism in the algorithm selected for a DSP application and the number of functional units. The throughput will be higher only if the algorithm involves execution of independent operations. For example, in convolution by using eight functional units, the time required can be reduced by a factor of 8 compared to the case where a single functional unit is used.

- However, it may not always be possible to have independent stream of data for processing. The number of functional units is also limited by the hardware cost for the multi-ported register file and cross bar switch.

## **Advantages of VLIW architecture**

- Increased performance.

- Potentially scalable i.e. more execution units can be added and so more instructions can be packed into the VLIW instruction.

## Disadvantages of VLIW architecture

- New programmer needed.

- Program must keep track of Instruction scheduling.

- Increased memory use.

- High power consumption.

# **ARM Processor**

• The ARM microcontroller stands for Advance Risk Machine; it is one of the extensive and most licensed processor cores in the world. The first ARM processor was developed in the year 1978 by Cambridge University, and the first ARM RISC processor was produced by the Acorn Group of Computers in the year 1985. These processors are specifically used in portable devices like digital cameras, mobile phones, home networking modules and wireless communication technologies and other embedded systems due to the benefits, such as low power consumption, reasonable performance, etc.

#### **ARM Architecture**

• The ARM architecture processor is an advanced reduced instruction set computing [RISC] machine and it's a 32bit reduced instruction set computer (RISC) microcontroller. It was introduced by the Acron computer organization in 1987. This ARM is a family of microcontroller developed by makers like ST Microelectronics, Motorola, and so on. The ARM architecture comes with totally different versions like ARMv1, ARMv2, etc.

#### **ARM Cortex:**

- The ARM cortex is a complicated microcontroller within the ARM family that has ARMv7 design. There are 3 subfamilies within the ARM cortex family:

- ARM Cortex Ax-series

- ARM-Cortex Rx-series

- ARM-Cortex Mx-series

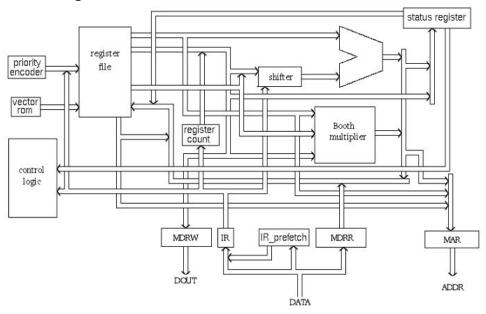

## ARM Block Diagram

• The ARM processor conjointly has other components like the Program status register, which contains the processor flags (Z, S, V and C). The modes bits conjointly exist within the program standing register, in addition to the interrupt and quick interrupt disable bits;

- Some special registers: Some registers are used like the instruction; memory data read and write registers and memory address register.

- Priority encoder: The encoder is used in the multiple load and store instruction to point which register within the register file to be loaded or kept.

- Multiplexers: several multiplexers are accustomed to the management operation of the processor buses. Because of the restricted project time, we tend to implement these components in a very behavioural model. Each component is described with an entity. Every entity has its own architecture, which can be optimized for certain necessities depending on its application. This creates the design easier to construct and maintain.

## **The ARM Architecture:**

The ARM processor consists of:

- Arithmetic Logic Unit

- Booth multiplier

- Barrel shifter

- Control unit

- Register file

### **Arithmetic Logic Unit (ALU)**

• The ALU has two 32-bits inputs. The primary comes from the register file, whereas the other comes from the shifter. Status registers flags modified by the ALU outputs. The V-bit output goes to the V flag as well as the Count goes to the C flag. Whereas the foremost significant bit really represents the S flag, the ALU output operation is done by NORed to get the Z flag. The ALU has a 4-bit function bus that permits up to 16 opcodes to be implemented.

### **Booth Multiplier Factor**

• The multiplier factor has 3 32-bit inputs and the inputs return from the register file. The multiplier output is barely 32-Least Significant Bits of the merchandise. The multiplication starts whenever the beginning 04 input goes active. Fin of the output goes high when finishing.

## **Booth Algorithm**

• Booth algorithm is a noteworthy multiplication algorithmic rule for 2's complement numbers. This treats positive and negative numbers uniformly. Moreover, the runs of 0's or 1's within the multiplier factor are skipped over without any addition or subtraction being performed, thereby creating possible quicker multiplication. The figure shows the simulation results for the multiplier test bench. It's clear that the multiplication finishes only in 16 clock cycle.

#### **Barrel Shifter**

- The barrel shifter features a 32-bit input to be shifted. This input is coming back from the register file or it might be immediate data. The shifter has different control inputs coming back from the instruction register. The Shift field within the instruction controls the operation of the barrel shifter. This field indicates the kind of shift to be performed (logical left or right, arithmetic right or rotate right). The quantity by which the register ought to be shifted is contained in an immediate field within the instruction or it might be the lower 6 bits of a register within the register file.

- The shift\_val input bus is 6-bits, permitting up to 32-bit shift. The shift type indicates the needed shift sort of 00, 01, 10, 11 are corresponding to shift left, shift right, an arithmetic shift right and rotate right, respectively. The barrel shifter is especially created with multiplexers.

#### **Control Unit**

• For any microprocessor, control unit is the heart of the whole process and it is responsible for the system operation, so the control unit design is the most important part within the whole design. The control unit is sometimes a pure combinational circuit design. Here, the control unit is implemented by easy state machine. The processor timing is additionally included within the control unit. Signals from the control unit are connected to each component within the processor to supervise its operation.

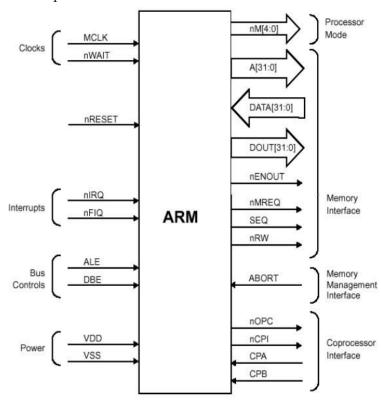

#### **ARM7 Functional Diagram**

The final thing that must be explained is how the ARM will be used and the way in which the chip appear. The various signals that interface with the processor are input, output or supervisory signals which will be used to control the ARM operation.

**ARM Functional Diagram**

#### **Additional Uses of the Cortex Processor**

- It is a reduced instruction set computing Controller having 32-bit high performance central processing unit and 3-stage pipeline and compact one.

- It has THUMB-2 technology

- Merges optimally with 16/32-bit instructions

- High performance

- It supports tools and RTOS and its core Sight debug and trace

- Support for multiple processors

- Low power Modes

- It supports sleep modes

- Control the software package

- Multiple power domains

- Nested vectored interrupt controller (NVIC)

- Low latency, low noise interrupts response

- No need for assembly programming

# **SPARC** processor

#### **Introduction:**

- SPARC stands for Scalable Processor Architecture.

- It is developed by Sun Microsystems in the 1980s.

- It is based on the RISC structure designed at the University of California at Berkeley in early 1980s.

- The SPARC architecture is a non-proprietary architecture that any person or company can license and use to develop microprocessors and other semiconductor devices based on published industry standards.

- In 1989, Sun Microsystems transferred ownership of the SPARC specifications to an independent, non-profit organization, SPARC International, which administers and licenses the technology and provides conformance testing and other services for its members.

## **Design Goals**

- SPARC was designed as a target for optimizing compilers and easily pipelined hardware implementations.

- SPARC implementations provide exceptionally high execution rates(MIPS) and short time-to-market development schedules.

- It provide the scalability of the cost/performance ratio of successive implementations with the current improvements in circuit technology.

- The "Scalable" in SPARC comes from the fact that the SPARC specification allows implementations to scale from processors required in embedded systems to processors used for servers.

## **Brief History:** 3 major revisions to the SPARC architecture

- SPARC-V7, 32bit, 1986

- SPARC-V8, 32bit, 1990

- SPARC-V9, 64bit, 1993

- In early 2006, Sun released an extended architecture specification, UltraSPARC Architecture 2005.

#### The SPARC Architecture

- It is a Load and store architecture. Operations are always done over registers.

- Uses "register window" concept thus offering a large number of registers.

- Uses delay slot to optimize branch instruction.

- Passes arguments using registers and the stack.

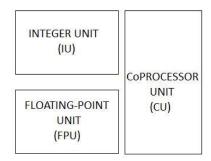

#### The Modules:

### 1) The Integer Unit (IU)

- Contains the general-purpose registers and controls the overall operation of the processor.

- It may contain from 64 to 528 general-purpose 64-bit r registers. They are partitioned into 8 global registers, 8 alternate global registers, plus a circular stack of from 3 to 32 sets of 16 registers each, known as register windows.

- Executes the integer arithmetic instructions and computes memory addresses for loads and stores.

- Maintains the program counters and controls instruction execution for the FPU.

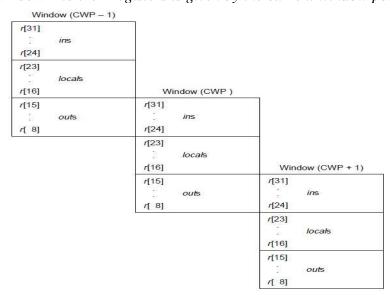

#### 2) The Register Window

- At any time, an instruction can access the 8 global registers and a 24-register window

- A register window comprises a 16-register set- divided into 8 in and 8 local registers- together with the 8 in registers of an adjacent register set, addressable from the current window as its out registers.

- When a procedure is called, the register window shifts by sixteen registers, hiding the old input registers and old local registers and making the old output registers the new input registers.

- o Input registers: arguments are passed to a function

- o Local registers: to store any local data.

- Output registers: When calling a function, the programmer puts his argument in these registers.

- The current window into the r registers is given by the current window pointer (CWP) register.

## 3) The Floating-point Unit (FPU)

- The FPU has 32 32-bit (single-precision) floating-point registers, 32 64-bit (double-precision) floating-point registers, and 16 128-bit (quad-precision) floating-point registers.

- Double-precision values occupy an even-odd pair of single-precision registers.

- Quad-precision values occupy an odd-even number of pair of double precision registers.

- Floating-point load/store instructions are used to move data between the FPU and memory.

- The memory address is calculated by the IU.

- Floating-Point operate (FPop) instructions perform the floating-point arithmetic operations and comparisons.

### 4) Coprocessor Unit (CU)

- The instruction set includes support for a single, implementation-dependent coprocessor. The coprocessor has its own set of registers.

- Coprocessor load/store instructions are used to move data between the coprocessor registers and memory.

#### 5) Instructions

Instructions can fall into following basic categories:

- Load/store

- Arithmetic/logical/shift

- Control transfer

- Read/write control register

- Floating-point/Coprocessor operate

## **SPARC v9 features**

- 64-bit Data and Addresses as compared to 32-bit Data and Addresses of SPARC V8.

- 32 double-precision floating-point registers,

- Software-settable branch prediction

- 64-bit integer multiply and divide instructions

- load/store floating-point quad word instructions

- Branches on register value (eliminating the need to compare)

- The V9 remains binary compatible with all previous SPARC architecture.

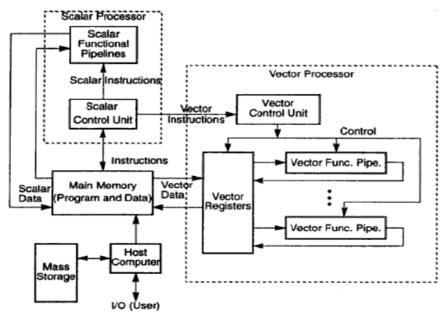

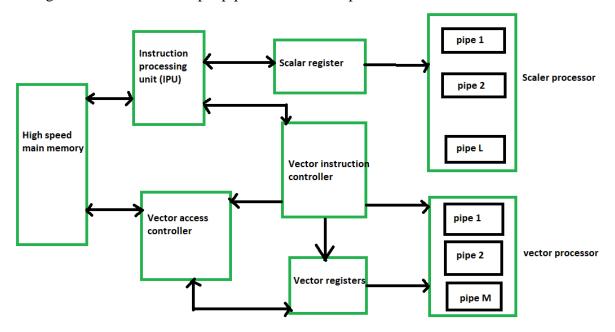

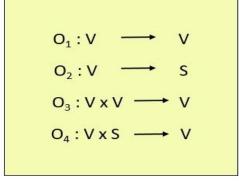

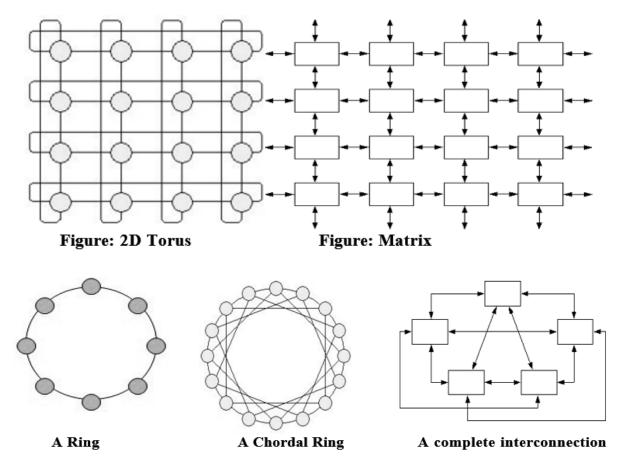

# Department of Computer Science and Engineering Subject Name: Advanced Computer Architecture UNIT-II

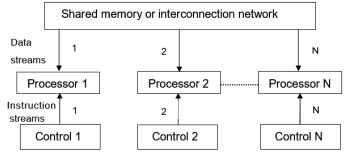

#### Flynn's Classification

Flynn's classification distinguishes multi-processor computer architectures according to two independent dimensions of Instruction stream and Data stream. An instruction stream is sequence of instructions executed by machine. And a data stream is a sequence of data including input, partial or temporary results used by instruction stream. Each of these dimensions can have only one of two possible states: Single or Multiple. Flynn's classification depends on the distinction between the performance of control unit and the data processing unit rather than its' operational and structural interconnections.

Following are the four category of Flynn classification and characteristic feature of each of them.

## 1. Single Instruction Stream, Single Data Stream (SISD)

The following figure represents an organization of simple SISD computer having one control unit, one processor unit and single memory unit.

## **SISD** processor organizations

- They are also called scalar processor i.e., one instruction at a time and each instruction have only one set of operands.

- Single instruction: only one instruction stream is being acted on by the CPU during any one clock cycle.

#### Characteristics:

- Single data: only one data stream is being used as input during any one clock cycle.

- Deterministic execution.

- Instructions are executed sequentially.

- This is the oldest and until recently, the most prevalent form of computer.

Example: most PCs, single CPU workstations and mainframes.

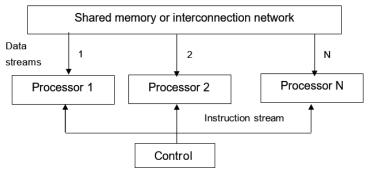

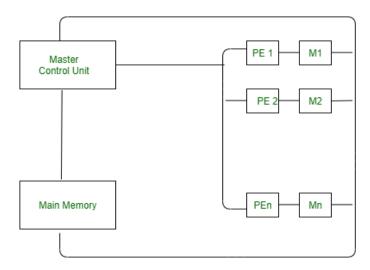

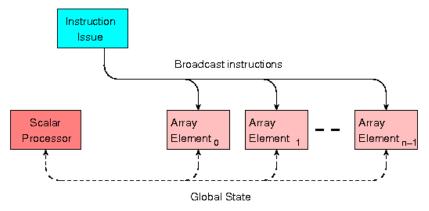

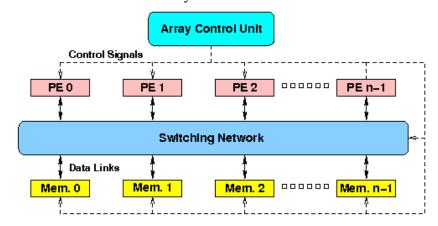

### 2. Single Instruction Stream, Multiple Data Stream (SIMD) processors

- This is a type of parallel computer.

- Single instruction: All processing units execute the same instruction issued by the control unit at any given clock cycle as shown in figure where there are multiple processors executing instruct ion given by one control unit.

- Multiple data: Each processing unit can operate on a different data element a s shown if figure below the processor are connected to shared memory or interconnection network providing multiple data to processing unit.

- This type of machine typically has an instruct ion dispatcher, a very high-bandwidth internal network, and a very large array of very small-capacity instruction units. Thus, single instruction is executed by different processing unit on different set of data.

- Best suited for specialized problems characterized by a high degree of regularity, such as image processing and vector computation.

- Synchronous (lockstep) and deterministic execution.

SIMD processor organizations

## 3. Multiple Instruction Stream, Single Data Stream (MISD)

- Here, a single data stream is feed into multiple processing units.

- Each processing unit operates on the data independently through independent instruction streams as shown in following figure a single data stream is forwarded to different processing unit which are connected to different control unit and execute instruction given to it by control unit to which it is attached.

Figure: MISD processor organizations

- Thus, in these computers same data flow through a linear array of processors executing different instruction streams.

- This architecture is also known as systolic arrays for pipelined execution of specific instructions.

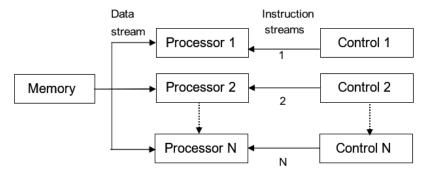

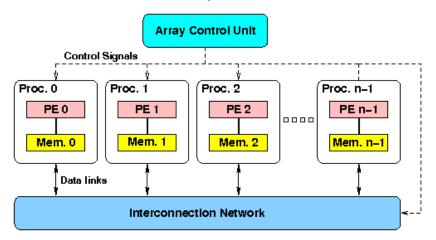

## 4. Multiple Instruction Stream, Multiple Data Stream (MIMD)

- Multiple Instructions: Every Processor may be executing a different instruction stream.

- Multiple Data: every processor may be working with a different data stream as shown in the figure multiple data stream is provided by shared memory.

- Can be categorized as loosely coupled or tightly coupled depending on sharing of data and control.

- Execution can be synchronous or asynchronous, deterministic or non- deterministic.

- Examples: most current supercomputers, networked parallel computer " grids" and multi-processor SMP computers including some types of PCs.

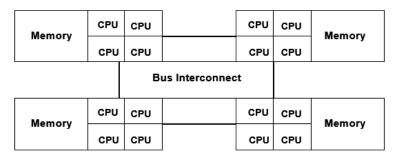

MIMD processor organizations System

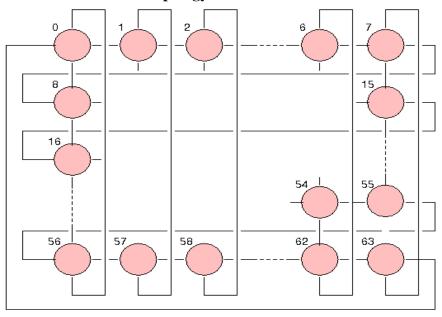

# **Parallel Computer Models**

# **Multiprocessor and Multicomputer**

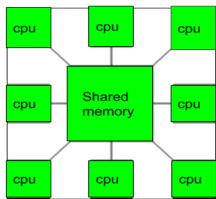

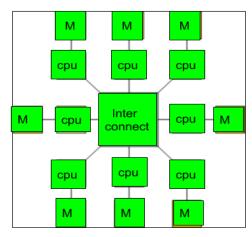

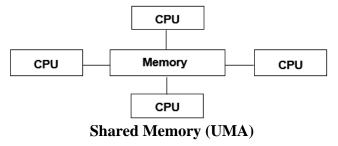

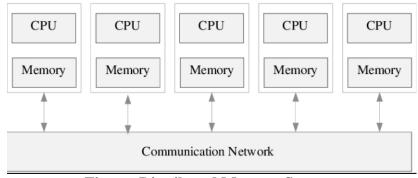

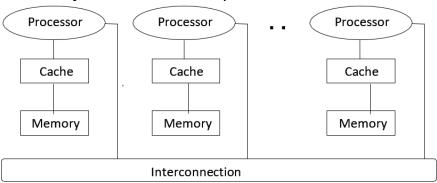

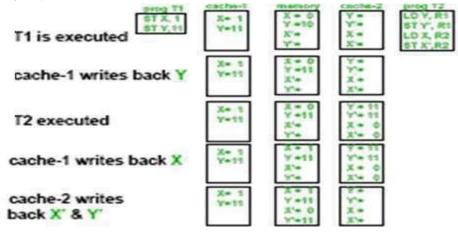

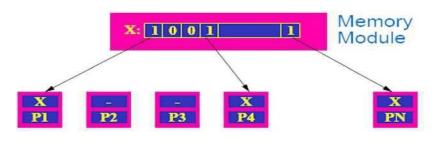

## 1. Multiprocessor:

- A Multiprocessor is a computer system with two or more central processing units (CPUs) share full access to a common RAM. The main objective of using a multiprocessor is to boost the system's execution speed, with other objectives being fault tolerance and application matching.

- There are two types of multiprocessors, one is called shared memory multiprocessor and another

is distributed memory multiprocessor. In shared memory multiprocessors, all the CPUs shares the

common memory but in a distributed memory multiprocessor, every CPU has its own private

memory.

## **Applications of Multiprocessor –**

- As a uniprocessor, such as single instruction, single data stream (SISD).

- As a multiprocessor, such as single instruction, multiple data stream (SIMD), which is usually used for vector processing.

- Multiple series of instructions in a single perspective, such as multiple instruction, single data stream (MISD), which is used for describing hyper-threading or pipelined processors.

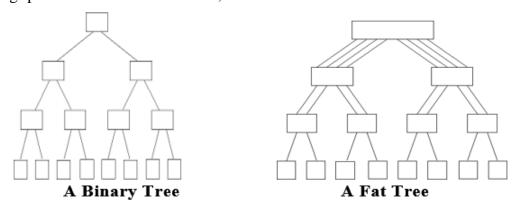

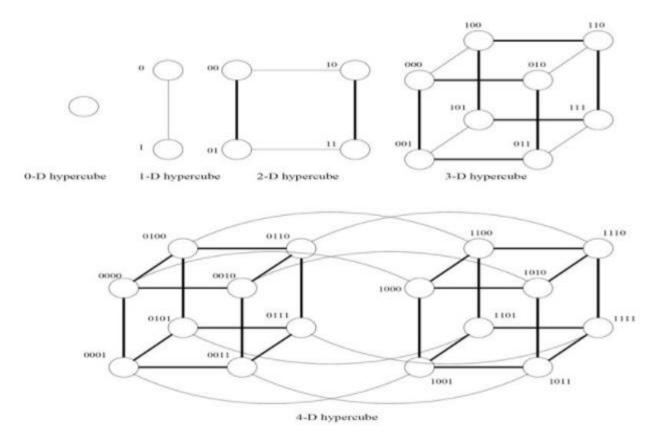

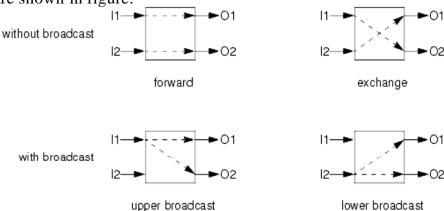

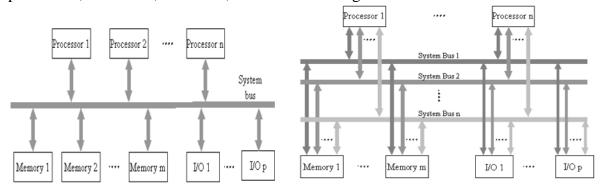

- Inside a single system for executing multiple, individual series of instructions in multiple perspectives, such as multiple instruction, multiple data stream (MIMD).